The continued development of large, high-speed digital computers has brought about a change in the relative importance of various techniques in the solution of large networks. Digital-computer solutions depend upon network equations So it is important that the power-system engineer understand the formulation of the equations from which, in obtaining a solution, the program that is followed by the computer is derived.

This chapter is not meant to be a comprehensive review of network equations but will serve to review and expand upon those methods of analysis upon which programs for computer solutions of power-system problems are very dependent.

Of particular importance in this chapter is the introduction of bus admittance and impedance matrices which will prove to be very useful in later work.

## 7.1 EQUIVALENCE OF SOURCES

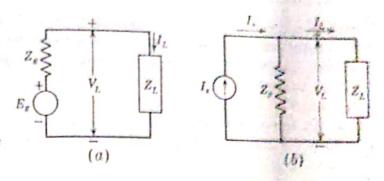

A helpful procedure in some problems in network analysis is the substitution of a source of constant current in parallel with an impedance for a constant end and series impedance. The two parts of Fig. 7.1 illustrate the circuits. Both sources with their assession to parts of Fig. 7.1 illustrate the circuits. sources with their associated impedances are connected to a two-terminal network having an input in network having an input impedances are connected to a two-two-network for the present all page 2. The load may be considered a page  $Z_L$ . network for the present; that is, any internal emfs in the load network as assumed to be short-circuited and any current sources opened.

Figure 7.1 Circuits illustrating the equivalence of sources.

For the circuit having the constant emf  $E_g$  and series impedance  $Z_g$ , the voltage across the load is

$$V_L = E_g - I_L Z_g \tag{7.1}$$

where IL is the load current. For the circuit having a source of constant current where  $I_L$  is shunt impedance  $Z_p$ , the voltage across the load is

$$V_L = (I_s - I_L)Z_p = I_s Z_p - I_L Z_p$$

(7.2)

The two sources and their associated impedances will be equivalent if the voltage  $V_L$  is the same in both circuits. Of course, equal values of  $V_L$  will mean equal load currents  $I_L$  for identical loads.

Comparison of Eqs. (7.1) and (7.2) shows that  $V_L$  will be identical in both circuits and therefore that the emf and its series impedance can be interchanged with the current source and its shunt impedance provided

$$E_g = I_s Z_p \tag{7.3}$$

and

$$Z_{q} = Z_{p} \tag{7.4}$$

These relations show that a constant-current source and shunt impedance can be replaced by a constant emf and series impedance if the emf is equal to the product of the constant current and the shunt impedance and if the series impedance equals the shunt impedance. Conversely, a constant emf and series impedance can be replaced by a constant-current source and shunt impedance if the shunt impedance is identical to the series impedance and if the constant current is equal to the value of the emf divided by its series impedance.

We have shown the conditions for equivalence of sources connected to a passive network. By considering the principle of superposition we can show that the same provisions apply if the output is an active network, that is, if the output network includes voltage and current sources. To determine the contribution from the supply if the output network is active, the principle of superposition calls for shorting emfs in the output network and replacing current sources by open circuits while impedances remain intact. Thus the output is a passive network so far as the current component from the interchangeable sources is toncerned. To determine the current components due to the sources in the load network, the emf of the supply source is shorted in one case and the current

source is opened in the other case. Thus, only Z<sub>0</sub> or its equivalent across the input to the load to determine the effect of source is the supply. nected across the input to the load to determine the effect of source is the supply. So in any to the sources is the supply. nected across the input to the load to describe the ellect of loading network regardless of which type of source is the supply, so in apply of supply so long as the series in the load for nected acronetwork regardless of which type in

network regardless of which type in

position, the components contributed by the sources in the load in

the load in

the constant-current contributed by the sources in the load in

the constant-current contributed by the sources in the load in

the constant-current contributed by the sources in the load in

the constant-current contributed by the sources in the load in

the constant-current contributed by the sources in the load in

the constant-current contributed by the sources in the load in

the contributed by the sources in the load in the load in

the contributed by the sources in the load position, the components contributed by the position, the components contributed by the independent of the type of supply so long as the series impedance in the shunt impedance of the constant-current source. Therefore of a supply whether the load network. independent of the type of supply and independent of the type of supply equals the shunt impedance of the constant-current source. Therefore of the constant of the source of the constant of the cons equals the shunt impedance or the constraint of the load network is active or he

The junctions formed when two or more pure elements (R, L, or C, or an element) are connected to each other at their terminal The junctions formed when two or more pursued to each other at their terminal at holds. Systematic formulation of equations determined at holds. source of voltage or current) are connected at their termined at their termined at hodes. Systematic formulation of equations determined at hodes applying Kirchhoff's current law is the basis of some excellent. called nodes. Systematic formulation circuit by applying Kirchhoff's current law is the basis of some excellent to the convenient to the c circuit by applying Kirchnon's current.

Description of power-system problems. Usually it is convenient to some excellent to some convenient to some connected and the connect puter solutions of power-system production points major nodes.

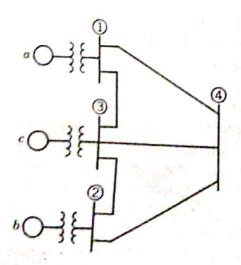

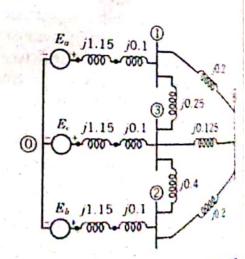

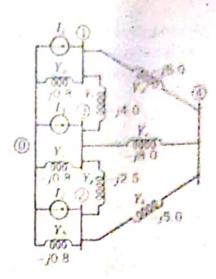

In order to examine some features of node equations, we shall begin a simple system shown in Fig. 7.2. Generators are In order to examine some learners one-line diagram of a simple system shown in Fig. 7.2. Generators are connected to high-tension buses 1 and 3 and supply a synthesis. through transformers to high-tension buses 1 and 3 and supply a synchronic through transformers at any or in the 2. For purposes of analysis, all machines at any or in the synchronic transformers. motor load at bus 2. For purposes of analysis, all machines at any one bus to machine and represented by a single emf and series treated as a single machine and represented by a single emf and series reaction with reactances specified in per unit, is shown The reactance diagram, with reactances specified in per unit, is shown in Fig. Nodes are indicated by dots, but numbers are assigned only to major node; the circuit is redrawn with the emfs and the impedances in series connecting them to the major nodes replaced by the equivalent current sources and the admittances, the result is the circuit of Fig. 7.4. Admittance values in per unit in

Figure 7.2 One-line diagram of a simple system.

Figure 7.3 Reactance diagram for the spare of Fig. 7.2. Reactance values are in per and

Figure 7.4 Circuit of Fig. 7.3 with current sources replacing the equivalent voltage sources. Values shown are admittances in per unit.

Single-subscript notation will be used to designate the voltage of each bus with respect to the neutral taken as the reference node 0. Applying Kirchhoff's current law at node 1 with current into the node from the source equated to current away from the node gives

$$I_1 = V_1 Y_a + (V_1 - V_3) Y_f + (V_1 - V_4) Y_d$$

(7.5)

and for node 4

$$0 = (V_4 - V_1)Y_d + (V_4 - V_2)Y_h + (V_4 - V_3)Y_e$$

(7.6)

Rearranging these equations yields

$$I_1 = V_1(Y_a + Y_f + Y_d) - V_3 Y_f - V_4 Y_d$$

(7.7)

$$0 = -V_1 Y_d - V_2 Y_h - V_3 Y_e + V_4 (Y_d + Y_e + Y_h)$$

(7.8)

Similar equations can be formed for nodes 2 and 3, and the four equations can be solved simultaneously for the voltages  $V_1$ ,  $V_2$ ,  $V_3$ , and  $V_4$ . All branch currents can be found when these voltages are known, and so the required number of node equations is one less than the number of nodes in the network. A node equation formed for the reference node would yield no further information. In other words, the number of independent node equations is one less than the number of nodes.

We have not written the other two equations because we can already see how to formulate node equations in standard notation. In both Eqs. (7.7) and (7.8) it is apparent that the current flowing into the network from current sources connected to a node is equated to the sum of several products. At any node one product is the voltage of that node times the sum of all the admittances which terminate on the node. This product accounts for the current that flows away from the node if the voltage is zero at each other node. Each other product equals the negative of the voltage at another node times the admittance connected directly between the other node and the node at which the equation is

formulated. For instance, at node 1 a product is  $-V_3 V_f$ , which accounts for independent equations in matrix at not formulated. For instance, at node 1 a production of the formulated form for the four independent equations in matrix form for the four independent equations in matrix form The standard form for the four independent equations in matrix form in

$$\begin{bmatrix} I_{1} \\ I_{2} \\ I_{3} \\ I_{4} \end{bmatrix} = \begin{bmatrix} Y_{11} & Y_{12} & Y_{13} & Y_{14} \\ Y_{21} & Y_{22} & Y_{23} & Y_{24} \\ Y_{31} & Y_{32} & Y_{33} & Y_{34} \\ Y_{41} & Y_{42} & Y_{43} & Y_{44} \end{bmatrix} \begin{bmatrix} V_{1} \\ V_{2} \\ V_{3} \\ V_{4} \end{bmatrix}$$

$$\begin{bmatrix} I_{1} \\ Y_{21} & Y_{12} & Y_{13} & Y_{14} \\ Y_{21} & Y_{22} & Y_{23} & Y_{24} \\ Y_{31} & Y_{32} & Y_{33} & Y_{34} \\ Y_{41} & Y_{42} & Y_{43} & Y_{44} \end{bmatrix} \begin{bmatrix} V_{1} \\ V_{2} \\ V_{3} \\ V_{4} \end{bmatrix}$$

The symmetry of the equations in this form makes them easy to remember to any number of nodes is apparent. The order of the  $\gamma$  substitute of  $\gamma$  substitute of the  $\gamma$  substitute of  $\gamma$  s The symmetry of the equations in the their extension to any number of nodes is apparent. The order of the  $\gamma$  subscript is that of the node at which the contribution of the symmetry of the equations in the equation in the equation of the equations in the equation of the equation o their extension to any number of the subscript is that of the node at which the current subscript is that of the voltage causing is effect-cause; that is, the most subscript is that of the voltage causing the being expressed, and the second subscript is that of the voltage causing the Y matrix is designated  $Y_{bus}$  and called the bus of the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is that of the voltage causing the second subscript is the second subscript is that of the voltage causing the second subscript is the is being expressed, and the second component of current. The Y matrix is designated  $Y_{bus}$  and called the bus administration of the symmetrical around the principal diagonal. The administration of the symmetrical around the principal diagonal. tance matrix.† It is symmetrical around the principal diagonal. The admittances at the nodes and tance matrix. The is symmetrical  $Y_{11}$ ,  $Y_{22}$ ,  $Y_{33}$ , and  $Y_{44}$  are called the self-admittances at the nodes, and each self-admittances terminating on the node identified to Y<sub>11</sub>, Y<sub>22</sub>, Y<sub>33</sub>, and Y<sub>44</sub> are called each equals the sum of all the admittances terminating on the node identified by the repeated subscripts. The other admittances are the mutual admittances of the nodes, and each equals the negative of the sum of all admittances connected directly between the nodes identified by the double subscripts. For the network of Fig. 7.4 the mutual admittance  $Y_{13}$  equals  $-Y_f$ . Some authors call the self. and mutual admittances of the nodes the driving-point and transfer admittances of the nodes.

The general expression for the source current toward node k of a network having N independent nodes, that is, N buses other than the neutral, is

$$I_{k} = \sum_{n=1}^{N} Y_{kn} V_{n} \tag{7.10}$$

One such equation must be written for each of the N buses at which the voltage of the network is unknown. If the voltage is fixed at any node, the equation is not written for that node. For instance, if both the magnitude and angle of the voltages at two of the high-tension buses of our example are fixed, only two equations are needed. Node equations would be written for the other two buses the only ones at which the voltage would be unknown. A known emf and series impedance need not be replaced by the equivalent current source if one terminal of the emf element is connected to the reference node, for then the node which separates the emf and series impedance is one where voltage is known.

Example 7.1 Write in matrix form the node equations necessary to solve for the voltages of the numbered buses of Fig. 7.4. The network is equivalent to that of Fig. 7.3. The emfs shown in Fig. 7.3 are  $E_a = 1.50$ .  $E_b = 1.5 \ / -36.87^{\circ}$ , and  $E_c = 1.5 / 0^{\circ}$ , all in per unit.

<sup>†</sup> Boldface type is used where one letter designates a matrix.

SOLUTION The current sources are

$$I_1 = I_3 = \frac{1.5/0^{\circ}}{j1.25} = 1.2 \angle -90^{\circ} = 0 - j1.20 \text{ per unit}$$

$$I_2 = \frac{1.5 \angle 36.87^{\circ}}{j1.25} = 1.2 \angle -126.87^{\circ} = -0.72 - j0.96 \text{ per unit}$$

Self-admittances in per unit are

$$Y_{11} = -j5.0 - j4.0 - j0.8 = -j9.8$$

$$Y_{22} = -j5.0 - j2.5 - j0.8 = -j8.3$$

$$Y_{33} = -j4.0 - j2.5 - j8.0 - j0.8 = -j15.3$$

$$Y_{44} = -j5.0 - j5.0 - j8.0 = -j18.0$$

and the mutual admittances in per unit are

$$Y_{12} = Y_{21} = 0$$

$Y_{23} = Y_{32} = +j2.5$

$Y_{13} = Y_{31} = +j4.0$   $Y_{24} = Y_{42} = +j5.0$

$Y_{14} = Y_{41} = +j5.0$   $Y_{34} = Y_{43} = +j8.0$

The node equations in matrix form are

$$\begin{bmatrix} 0 & -j1.20 \\ -0.72 - j0.96 \\ 0 & -j1.20 \\ 0 \end{bmatrix} = \begin{bmatrix} -j9.8 & j0.0 & j4.0 & j5.0 \\ j0.0 & -j8.3 & j2.5 & j5.0 \\ j4.0 & j2.5 & -j15.3 & j8.0 \\ j5.0 & j5.0 & j8.0 & -j18.0 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \end{bmatrix}$$

The square matrix above is recognized as the bus admittance matrix Y bus.

Example 7.2 Solve the node equations of the preceding example to find the bus voltages by inverting the bus admittance matrix.

SOLUTION Premultiplying both sides of the matrix equation of Example 7.1 by the inverse of the bus admittance matrix (determined by using a standard program on a digital computer) yields

$$\begin{bmatrix} j0.4774 & j0.3706 & j0.4020 & j0.4142 \\ j0.3706 & j0.4872 & j0.3922 & j0.4126 \\ j0.4020 & j0.3922 & j0.4558 & j0.4232 \\ j0.4142 & j0.4126 & j0.4232 & j0.4733 \end{bmatrix} \begin{bmatrix} 0 & -j1.20 \\ -0.72 - j0.96 \\ 0 & -j1.20 \\ 0 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \end{bmatrix}$$

The square matrix above obtained by inverting the bus admittance matrix is

called the bus impedance matrix Z<sub>bus</sub>. Performing the indicated in the in

$$\begin{bmatrix} 1.4111 - j0.2668 \\ 1.3830 - j0.3508 \\ 1.4059 - j0.2824 \\ 1.4009 - j0.2971 \end{bmatrix} = \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \end{bmatrix}$$

and so the node voltages are

$$V_1 = 1.4111 - j0.2668 = 1.436 / -10.71^{\circ}$$

per unit  $V_2 = 1.3830 - j0.3508 = 1.427 / -14.24^{\circ}$  per unit  $V_3 = 1.4059 - j0.2824 = 1.434 / -11.36^{\circ}$  per unit  $V_4 = 1.4009 - j0.2971 = 1.432 / -11.97^{\circ}$  per unit

#### 7.3 MATRIX PARTITIONING

A useful method of matrix manipulation, called partitioning, consists in temps. ing various parts of a matrix as submatrices which are treated as single clean in applying the usual rules of multiplication and addition. For instance, was

$$\mathbf{A} = \begin{bmatrix} a_{11} & a_{12} & a_{13} \\ a_{21} & a_{22} & a_{23} \\ \hline a_{31} & a_{32} & a_{33} \end{bmatrix} \tag{11}$$

The matrix is partitioned into four submatrices by the horizontal and venice dashed lines. The matrix may be written

$$A = \begin{bmatrix} D & E \\ F & G \end{bmatrix}$$

where the submatrices are

$$D = \begin{bmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \end{bmatrix} \qquad \mathbf{E} = \begin{bmatrix} a_{13} \\ a_{23} \end{bmatrix}$$

$$\mathbf{F} = \begin{bmatrix} a_{31} & a_{32} \end{bmatrix} \qquad \mathbf{G} = a_{23}$$

To show the steps in matrix multiplication in terms of submatrices kinds assume that A is to be postmultiplied by another matrix B to form the postmultiplied

$$\mathbf{B} = \begin{bmatrix} b_{11} \\ b_{21} \\ \vdots \\ b_{31} \end{bmatrix} \tag{7.13}$$

With partitioning as indicated,

$$\mathbf{B} = \begin{bmatrix} \mathbf{H} \\ \mathbf{J} \end{bmatrix} \tag{7.14}$$

where the submatrices are

$$\mathbf{H} = \begin{bmatrix} b_{11} \\ b_{21} \end{bmatrix} \quad \text{and} \quad \mathbf{J} = b_{31}$$

Then the product is

$$C = AB = \begin{bmatrix} D & E \\ F & G \end{bmatrix} \begin{bmatrix} H \\ J \end{bmatrix}$$

(7.15)

The submatrices are treated as single elements to obtain

$$C = \begin{bmatrix} DH + EJ \\ FH + GJ \end{bmatrix}$$

(7.16)

The product is finally determined by performing the indicated multiplication and addition of the submatrices.

If C is composed of the submatrices M and N so that

$$C = \begin{bmatrix} M \\ N \end{bmatrix} \tag{7.17}$$

comparison with Eq. (7.16) shows

$$M = DH + EJ \tag{7.18}$$

$$N = FH + GJ \tag{7.19}$$

If we wish to find only the submatrix N, partitioning shows that

$$N = \begin{bmatrix} a_{31} & a_{32} \end{bmatrix} \begin{bmatrix} b_{11} \\ b_{21} \end{bmatrix} + a_{33}b_{31}$$

$$= a_{31}b_{11} + a_{32}b_{21} + a_{33}b_{31}$$

(7.20)

The matrices to be multiplied must be compatible originally. Each vertical partitioning line between columns r and r+1 of the first factor requires a horizontal partitioning line between rows r and r+1 of the second factor in order for the submatrices to be multiplied. Horizontal partitioning lines may be drawn between any rows of the first factor, and vertical lines between any columns of the second, or omitted in either or both. An example that applies matrix partitioning appears at the end of the next section.

### 7.4 NODE ELIMINATION BY MATRIX ALGEBRA

Nodes may be eliminated by matrix manipulation of the standard node equa. Nodes may be eliminated by indicate the state of leave the tions. However, only those nodes at which current does not enter or leave the

The standard node equations in matrix notation are expressed as

$$I = Y_{bus}V$$

and  $Y_{bus}$  is a symmetrical (7.21)

where I and V are column matrices and Y<sub>bus</sub> is a symmetrical square matrix. The column matrices must be so arranged that elements associated with nodes to be eliminated are in the lower rows of the matrices. Elements of the square admit. tance matrix are located correspondingly. The column matrices are partitioned so that the elements associated with nodes to be eliminated are separated from the other elements. The admittance matrix is partitioned so that elements identified only with nodes to be eliminated are separated from the other elements by horizontal and vertical lines. When partitioned according to these rules, Eq. (7.21) becomes

$$\begin{bmatrix} \mathbf{I}_{A} \\ \mathbf{I}_{X} \end{bmatrix} = \begin{bmatrix} \mathbf{K} & \mathbf{L} \\ \mathbf{L}^{T} & \mathbf{M} \end{bmatrix} \begin{bmatrix} \mathbf{V}_{A} \\ \mathbf{V}_{X} \end{bmatrix}$$

(7.22)

where  $I_X$  is the submatrix composed of the currents entering the nodes to be eliminated and  $V_{\chi}$  is the submatrix composed of the voltages of these nodes. Of course, every element in  $I_x$  is zero, for the nodes could not be eliminated otherwise. The self- and mutual admittances composing K are those identified only with nodes to be retained. M is composed of the self- and mutual admittances identified only with nodes to be eliminated. It is a square matrix whose order is equal to the number of nodes to be eliminated. L and its transpose L' are composed of only those mutual admittances common to a node to be retained and to one to be eliminated.

Performing the multiplication indicated in Eq. (7.22) gives

$$I_A = KV_A + LV_X \tag{7.23}$$

and

$$\mathbf{I}_X = \mathbf{L}^T \mathbf{V}_A + \mathbf{M} \mathbf{V}_X \tag{7.24}$$

Since all elements of  $I_X$  are zero, subtracting  $L^TV_A$  from both sides of Eq. (7.24) and multiplying both sides by the inverse of M (denoted by  $M^{-1}$ ) yields

$$-\mathbf{M}^{-1}\mathbf{L}^{T}\mathbf{V}_{A} = \mathbf{V}_{X} \tag{7.25}$$

This expression for  $V_X$  substituted in Eq. (7.23) gives

$$\mathbf{I}_{A} = \mathbf{K} \mathbf{V}_{A} - \mathbf{L} \mathbf{M}^{-1} \mathbf{L}^{T} \mathbf{V}_{A} \tag{7.26}$$

which is a node equation having the admittance matrix

$$\mathbf{Y}_{\text{bus}} = \mathbf{K} - \mathbf{L} \mathbf{M}^{-1} \mathbf{L}^{T} \tag{7.27}$$

This admittance matrix enables us to construct the circuit with the unwanted nodes eliminated, as we shall see in the following example.

Example 7.3 If the generator and transformer at bus 3 are removed from the circuit of Fig. 7.3, eliminate node 3 and 4 by the matrix-algebra procedure just described, find the equivalent circuit with these nodes eliminated, and find the complex power transferred into or out of the network at nodes I and 2. Also find the voltage at node 1.

SOLUTION The bus admittance matrix of the circuit partitioned for elimination of nodes 3 and 4 is

$$\mathbf{Y}_{\text{bus}} = \begin{bmatrix} \mathbf{K} & \mathbf{L} \\ \mathbf{L}^T & \mathbf{M} \end{bmatrix} = \begin{bmatrix} -j9.8 & 0.0 & j4.0 & j5.0 \\ 0.0 & -j8.3 & j2.5 & j5.0 \\ j4.0 & j2.5 & -j14.5 & j8.0 \\ j5.0 & j5.0 & j8.0 & -j18.0 \end{bmatrix}$$

The inverse of the submatrix in the lower right position is

$$\mathbf{M}^{-1} = \frac{1}{-197} \begin{bmatrix} -j18.0 & -j8.0 \\ -j8.0 & -j14.5 \end{bmatrix} = \begin{bmatrix} j0.0914 & j0.0406 \\ j0.0406 & j0.0736 \end{bmatrix}$$

Then

$$\mathbf{L}\mathbf{M}^{-1}\mathbf{L}^{T} = \begin{bmatrix} j4.0 & j5.0 \\ j2.5 & j5.0 \end{bmatrix} \begin{bmatrix} j0.0914 & j0.0406 \\ j0.0406 & j0.0736 \end{bmatrix} \begin{bmatrix} j4.0 & j2.5 \\ j5.0 & j5.0 \end{bmatrix}$$

$$= -\begin{bmatrix} j4.9264 & j4.0736 \\ j4.0736 & j3.4264 \end{bmatrix}$$

$$\mathbf{Y}_{\text{bus}} = \mathbf{K} - \mathbf{L}\mathbf{M}^{-1}\mathbf{L}^{T} = \begin{bmatrix} -j9.8 & 0.0 \\ 0.0 & -j8.3 \end{bmatrix} - \mathbf{L}\mathbf{M}^{-1}\mathbf{L}^{T}$$

$$\mathbf{Y}_{\text{bus}} = \begin{bmatrix} -j4.8736 & j4.0736 \\ j4.0736 & -j4.8736 \end{bmatrix}$$

Examination of the matrix shows us that the admittance between the two remaining buses 1 and 2 is -j4.0736, the reciprocal of which is the per-unit impedance between these buses. The admittance between each of these buses and the reference bus is

$$-j4.8736 - (-j4.0736) = -j0.800$$

per unit

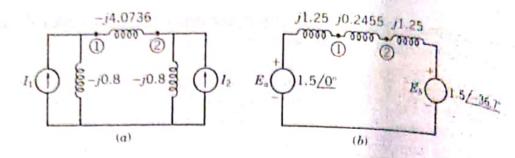

The resulting circuit is shown in Fig. 7.5a. When the current sources are converted to their equivalent emf sources the circuit, with impedances in per unit, is that of Fig. 7.5b. Then the current is

$$I = \frac{1.5/0^{\circ} - 1.5/-36.87^{\circ}}{j(1.25 + 1.25 + 0.2455)} = \frac{1.5 - 1.2 + j0.9}{j(2.7455)}$$

$$= 0.3278 - j0.1093 = 0.3455 \angle 18.44 \text{ per unit}$$

Figure 7.5 Circuit of Fig. 7.3 without the source at node 3 (a) with the equivalent current sources and (b) with the original voltage sources at nodes 1 and 2.

Power out of source a is

$$1.5/0^{\circ} \times 0.3455/18.44^{\circ} = 0.492 + j0.164$$

per unit

And power into source b is

$$1.5 / -36.87^{\circ} \times 0.3455 / 18.44^{\circ} = 0.492 - j0.164$$

per unit

Note that the reactive voltamperes in the circuit equal

$$(0.3455)^2 \times 2.7455 = 0.328 = 0.164 + 0.164$$

The voltage at node 1 is

$$1.50 - j1.25(0.3278 - j0.1093) = 1.363 - j0.410$$

per unit

In the simple circuit of this example node elimination could have been accomplished by  $Y-\Delta$  transformations and by working with series and parallel combinations of impedances. The matrix partitioning method is a general method which is thereby more suitable for computer solutions. However, for the elimination of a large number of nodes, the matrix M whose inverse must be found will be large.

Inverting a matrix is avoided by eliminating one node at a time, and the process is very simple. The node to be eliminated must be the highest numbered node, and renumbering may be required. The matrix M becomes a single element and  $M^{-1}$  is the reciprocal of the element. The original admittance matrix partitioned into submatrices K, L,  $L^T$ , and M is

$$\mathbf{Y_{hus}} = \begin{bmatrix} \mathbf{X} \\ Y_{11} & \cdots & Y_{1j} & \cdots \\ Y_{k1} & \cdots & Y_{kj} & \cdots \\ \vdots & \vdots & \ddots & \vdots \\ Y_{n1} & \cdots & Y_{nj} & \cdots & Y_{nn} \end{bmatrix}$$

$$\mathbf{L}$$

$$(7.28)$$

the reduced  $(n-1) \times (n-1)$  matrix will be, according to Eq. (7.27),

$$\mathbf{Y}_{\text{bus}} = \begin{bmatrix} Y_{11} & \cdots & Y_{1j} & \cdots \\ \vdots & & \vdots & & \\ Y_{k1} & \cdots & Y_{kj} & \cdots \\ \vdots & & \vdots & & \end{bmatrix} - \frac{1}{Y_{nn}} \begin{bmatrix} Y_{1n} \\ Y_{kn} \\ \vdots \\ \vdots \end{bmatrix} [Y_{n1} \cdots Y_{nj} \cdots] \quad (7.29)$$

and when the indicated manipulation of the matrices is accomplished, the element in row k and column j of the resulting  $(n-1) \times (n-1)$  matrix will be

$$Y_{kj \text{ (new)}} = Y_{kj \text{ (orig)}} - \frac{Y_{kn} Y_{nj}}{Y_{nn}}$$

(7.30)

Each element in the original matrix K must be modified. When Eq. (7.28) is compared to Eq. (7.30) we can see how to proceed. We multiply the element in the last column and the same row as the element being modified by the element in the last row and the same column as the element being modified. We then divide this product by  $Y_{nn}$  and subtract the result from the element being modified. The following example illustrates the simple procedure.

Example 7.4 Perform the node elimination of Example 7.3 by first removing node 4 and then by removing node 3.

SOLUTION As in Example 7.3, the original matrix now partitioned for removal of one node is

$$\mathbf{Y_{bus}} = \begin{bmatrix} -j9.8 & 0.0 & j4.0 & j5.0 \\ 0.0 & -j8.3 & j2.5 & j5.0 \\ j4.0 & (j2.5) & -j14.5 & [j8.0] \\ \hline j5.0 & [j5.0] & j8.0 & -j18.0 \end{bmatrix}$$

To modify the element j2.5 in row 3, column 2 subtract from it the product of the elements enclosed by rectangles and divided by the element in the lower right corner. We find the modified element

$$Y_{32} = j2.5 - \frac{j8.0 \times j5.0}{-j18.0} = j4.7222$$

Similarly the new element in row 1, column 1 is

$$Y_{11} = -j9.8 - \frac{j5.0 \times j5.0}{-j18.0} = -j8.4111$$

Other elements are found in the same manner to yield

$$\mathbf{Y}_{\text{bus}} = \begin{bmatrix} -j8.4111 & j1.3889 & j6.2222\\ j1.3889 & -j6.9111 & j4.7222\\ j6.2222 & j4.7222 & -j10.9444 \end{bmatrix}$$

Reducing the above matrix to remove node 3 yields

$$\mathbf{Y}_{\text{bus}} = \begin{bmatrix} -j4.8736 & j4.0736 \\ j4.0736 & -j4.8736 \end{bmatrix}$$

which is identical to the matrix found by the matrix-partitioning method where two nodes were removed at the same time.

# 7.5 THE BUS ADMITTANCE AND IMPEDANCE MATRICES

In Example 7.2, we inverted the bus admittance matrix  $Y_{bus}$  and called the resultant matrix the bus impedance matrix  $Z_{bus}$ . By definition

$$Z_{\text{bus}} = Y_{\text{bus}}^{-1} \tag{7.31}$$

and for a network of three independent nodes

$$\mathbf{Z}_{\text{bus}} = \begin{bmatrix} Z_{11} & Z_{12} & Z_{13} \\ Z_{21} & Z_{22} & Z_{23} \\ Z_{31} & Z_{32} & Z_{33} \end{bmatrix}$$

(7.32)

Since  $Y_{bus}$  is symmetrical around the principal diagonal,  $Z_{bus}$  must be symmetrical in the same manner.

The impedance elements of Z<sub>bus</sub> on the principal diagonal are called drivingpoint impedance of the nodes, and the off-diagonal elements are called the transfer impedances of the nodes.

The bus admittance matrix need not be determined in order to obtain  $Z_{bus}$ , and in another section of this chapter we shall see how  $Z_{bus}$  may be formulated directly.

The bus impedance matrix is important and very useful in making fault calculations as we shall see later. In order to understand the physical significance of the various impedances in the matrix we shall compare them with the node admittances. We can easily do so by looking at the equations at a particular node. For instance, starting with the node equations expressed as

$$I = Y_{\text{bus}} V \tag{7.33}$$

we have at node 2 of the three independent nodes

$$I_2 = Y_{21} V_1 + Y_{22} V_2 + Y_{23} V_3 \tag{7.34}$$