## 5

# Semiconductor Physics

- 5.1 Semiconductor

- 5.2 Bonds in Semiconductors

- 5.3 Crystals

- 5.4 Commonly Used Semiconductors

- 5.5 Energy Band Description of Semiconductors

- 5.6 Effect of Temperature on Semiconductors

- 5.7 Hole Current

- 5.8 Intrinsic Semiconductor

- 5.9 Extrinsic Semiconductor

- 5.10 *n*-type Semiconductor

- 5.11 *p*-type Semiconductor

- 5.12 Charge on *n*-type and *p*-type Semiconductors

- 5.13 Majority and Minority Carriers

- 5.14 pn Junction

- 5.15 Properties of *pn*-Junction

- 5.16 Applying D.C. Voltage across *pn*-Junction or Biasing a *pn*-Junction

- 5.17 Current Flow in a Forward Biased *pn*-Junction

- 5.18 Volt-Ampere Characteristics of *pn*Junction

- 5.19 Important Terms

- **5.20** Limitations in the Operating Conditions of *pn*-Junction

#### INTRODUCTION

ertain substances like germanium, silicon, carbon etc. are neither good conductors like copper nor insulators like glass. In other words, the resistivity of these materials lies inbetween conductors and insulators. Such substances are classified as *semiconductors*. Semiconductors have some useful properties and are being extensively used in electronic circuits. For instance, *transistor*—a semiconductor device is fast replacing bulky vacuum tubes in almost all applications. Transistors are only one of the family of semiconductor devices are becoming increasingly popular. In this chapter, we shall focus our attention on the different aspects of semiconductors.

#### 5.1 Semiconductor

It is not easy to define a semiconductor if we want to take into account all its physical characteristics. However, generally, a semiconductor is defined on the basis of electrical conductivity as under:

A semiconductor is a substance which has resistivity ( $10^{-4}$  to 0.5  $\Omega m$ ) inbetween conductors and insulators e.g. germanium, silicon, selenium, carbon etc.

The reader may wonder, when a semiconductor is neither a good conductor nor an insulator, then why not to classify it as a *resistance material*? The answer shall be readily available if we study the following table:

| S.No. | Substance | Nature              | Resistivity                           |  |

|-------|-----------|---------------------|---------------------------------------|--|

| 1     | Copper    | good conductor      | $1.7 \times 10^{-8} \Omega \text{ m}$ |  |

| 2     | Germanium | semiconductor       | 0.6 Ω m                               |  |

| 3     | Glass     | insulator           | $9 \times 10^{11} \Omega \text{ m}$   |  |

| 4     | Nichrome  | resistance material | $10^{-4} \Omega$ m                    |  |

Comparing the resistivities of above materials, it is apparent that the resistivity of germanium (semiconductor) is quite high as compared to copper (conductor) but it is quite low when compared with glass (insulator). This shows that resistivity of a semiconductor lies inbetween conductors and insulators. However, it will be wrong to consider the semiconductor as a resistance material. For example, nichrome, which is one of the highest resistance material, has resistivity much lower than germanium. This shows that electrically germanium cannot be regarded as a conductor or insulator or a resistance material. This gave such substances like germanium the name of semiconductors.

It is interesting to note that it is not the resistivity alone that decides whether a substance is semiconductor or not. For example, it is just possible to prepare an alloy whose resistivity falls within the range of semiconductors but the alloy cannot be regarded as a semiconductor. In fact, semiconductors have a number of peculiar properties which distinguish them from conductors, insulators and resistance materials.

#### **Properties of Semiconductors**

- (i) The resistivity of a semiconductor is less than an insulator but more than a conductor.

- (ii) Semiconductors have *negative temperature co-efficient of resistance i.e.* the resistance of a semiconductor decreases with the increase in temperature and *vice-versa*. For example, germanium is actually an insulator at low temperatures but it becomes a good conductor at high temperatures.

- (iii) When a suitable metallic impurity (e.g. arsenic, gallium etc.) is added to a semiconductor, its current conducting properties change appreciably. This property is most important and is discussed later in detail.

#### 5.2 Bonds in Semiconductors

The atoms of every element are held together by the bonding action of valence electrons. This bonding is due to the fact that it is the tendency of each atom to complete its last orbit by acquiring 8 electrons in it. However, in most of the substances, the last orbit is incomplete *i.e.* the last orbit does not have 8 electrons. This makes the atom active to enter into bargain with other atoms to acquire 8 electrons in the last orbit. To do so, the atom may lose, gain or share valence electrons with other atoms. In semiconductors, bonds are formed by sharing of valence electrons. Such bonds are called *co-valent bonds*. In the formation of a co-valent bond, each atom contributes equal number of valence electrons and the contributed electrons are shared by the atoms engaged in the formation of the bond.

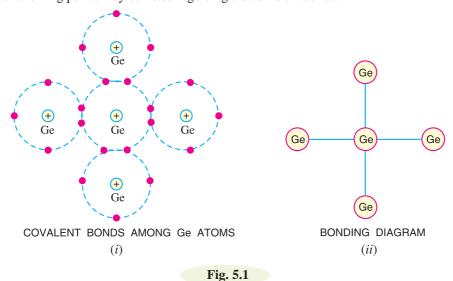

Fig. 5.1 shows the co-valent bonds among germanium atoms. A germanium atom has \*4 valence electrons. It is the tendency of each germanium atom to have 8 electrons in the last orbit. To do so, each germanium atom positions itself between four other germanium atoms as shown in Fig. 5.1 (i). Each neighbouring atom shares one valence electron with the central atom. In this business of sharing, the central atom completes its last orbit by having 8 electrons revolving around the nucleus. In this way, the central atom sets up co-valent bonds. Fig. 5.1 (ii) shows the bonding diagram.

The following points may be noted regarding the co-valent bonds:

- (i) Co-valent bonds are formed by sharing of valence electrons.

- (ii) In the formation of co-valent bond, each valence electron of an atom forms direct bond with the valence electron of an adjacent atom. In other words, valence electrons are associated with particular atoms. For this reason, valence electrons in a semiconductor are not free.

#### 5.3 Crystals

A substance in which the atoms or molecules are arranged in an orderly pattern is known as a *crystal*. All semi-conductors have crystalline structure. For example, referring to Fig. 5.1, it is clear that each atom is surrounded by neighbouring atoms in a repetitive manner. Therefore, a piece of germanium is generally called germanium crystal.

#### 5.4 Commonly Used Semiconductors

There are many semiconductors available, but very few of them have a practical application in electronics. The two most frequently used materials are *germanium* (Ge) and *silicon* (Si).

**Bonds in Semiconductor**

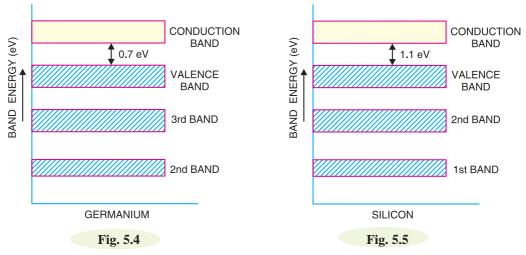

quently used materials are *germanium* (Ge) and *silicon* (Si). It is because the energy required to break their co-valent bonds (*i.e.* energy required to release an electron from their valence bands) is very small; being about 0.7 eV for germanium and about 1.1 eV for silicon. Therefore, we shall discuss these two semiconductors in detail.

\* A germanium atom has 32 electrons. First orbit has 2 electrons, second 8 electrons, third 18 electrons and the fourth orbit has 4 electrons.

(i) Germanium. Germanium has become the model substance among the semiconductors; the main reason being that it can be purified relatively well and crystallised easily. Germanium is an earth element and was discovered in 1886. It is recovered from the ash of certain coals or from the flue dust of zinc smelters. Generally, recovered germanium is in the form of germanium dioxide powder which is then reduced to pure germanium.

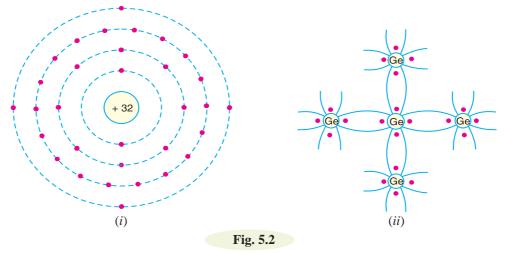

The atomic number of germanium is 32. Therefore, it has 32 protons and 32 electrons. Two electrons are in the first orbit, eight electrons in the second, eighteen electrons in the third and four electrons in the outer or valence orbit [See Fig. 5.2 (i)]. It is clear that germanium atom has four valence electrons i.e., it is a tetravalent element. Fig. 5.2 (ii) shows how the various germanium atoms are held through co-valent bonds. As the atoms are arranged in an orderly pattern, therefore, germanium has crystalline structure.

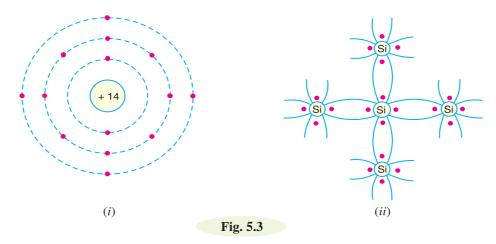

(ii) Silicon. Silicon is an element in most of the common rocks. Actually, sand is silicon dioxide. The silicon compounds are chemically reduced to silicon which is 100% pure for use as a semiconductor.

The atomic number of silicon is 14. Therefore, it has 14 protons and 14 electrons. Two electrons are in the first orbit, eight electrons in the second orbit and four electrons in the third orbit [See Fig. 5.3 (i)]. It is clear that silicon atom has four valence electrons i.e. it is a tetravalent element. Fig. 5.3 (ii) shows how various silicon atoms are held through co-valent bonds. Like germanium, silicon atoms are also arranged in an orderly manner. Therefore, silicon has crystalline structure.

#### 5.5 Energy Band Description of Semiconductors

It has already been discussed that a semiconductor is a substance whose resistivity lies between conductors and insulators. The resistivity is of the order of  $10^{-4}$  to 0.5 ohm metre. However, a semiconductor can be defined much more comprehensively on the basis of energy bands as under:

A semiconductor is a substance which has almost filled valence band and nearly empty conduction band with a very small energy gap ( $\simeq 1 \text{ eV}$ ) separating the two.

Figs. 5.4 and 5.5 show the energy band diagrams of germanium and silicon respectively. It may be seen that forbidden energy gap is very small; being 1.1 eV for silicon and 0.7 eV for germanium. Therefore, relatively small energy is needed by their valence electrons to cross over to the conduction band. Even at room temperature, some of the valence electrons may acquire sufficient energy to enter into the conduction band and thus become free electrons. However, at this temperature, the number of free electrons available is very \*small. Therefore, at room temperature, a piece of germanium or silicon is neither a good conductor nor an insulator. For this reason, such substances are called semiconductors.

The energy band description is extremely helpful in understanding the current flow through a semiconductor. Therefore, we shall frequently use this concept in our further discussion.

#### 5.6 Effect of Temperature on Semiconductors

The electrical conductivity of a semiconductor changes appreciably with temperature variations. This is a very important point to keep in mind.

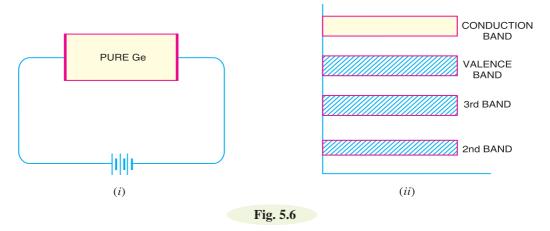

(i) At absolute zero. At absolute zero temperature, all the electrons are tightly held by the semiconductor atoms. The inner orbit electrons are bound whereas the valence electrons are engaged in co-valent bonding. At this temperature, the co-valent bonds are very strong and there are no free electrons. Therefore, the semiconductor crystal behaves as a perfect insulator [See Fig. 5.6 (i)].

In terms of energy band description, the valence band is filled and there is a large energy gap between valence band and conduction band. Therefore, no valence electron can reach the conduction band to become free electron. It is due to the non-availability of free electrons that a semiconductor behaves as an insulator.

Out of 10<sup>10</sup> semiconductor atoms, one atom provides a free electron.

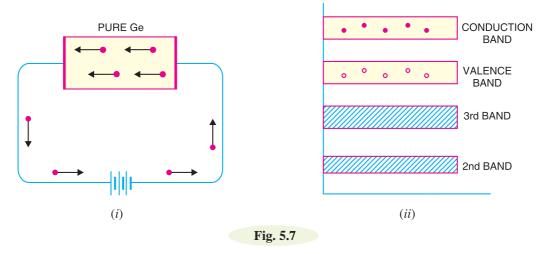

(ii) Above absolute zero. When the temperature is raised, some of the covalent bonds in the semiconductor break due to the thermal energy supplied. The breaking of bonds sets those electrons *free* which are engaged in the formation of these bonds. The result is that a few free electrons exist in the semiconductor. These free electrons can constitute a tiny electric current if potential difference is

applied across the semiconductor crystal [See Fig. 5.7 (i)]. This shows that the resistance of a semi-conductor decreases with the rise in temperature i.e. it has negative temperature coefficient of resistance. It may be added that at room temperature, current through a semiconductor is too small to be of any practical value.

Fig. 5.7 (ii) shows the energy band diagram. As the temperature is raised, some of the valence electrons acquire sufficient energy to enter into the conduction band and thus become free electrons. Under the influence of electric field, these free electrons will constitute electric current. It may be noted that each time a valence electron enters into the conduction band, a *hole* is created in the valence band. As we shall see in the next article, holes also contribute to current. In fact, hole current is the most significant concept in semiconductors.

#### 5.7 Hole Current

At room temperature, some of the co-valent bonds in pure semiconductor break, setting up free electrons. Under the influence of electric field, these free electrons constitute electric current. At the

same time, another current – the hole current – also flows in the semiconductor. When a covalent bond is broken due to thermal energy, the removal of one electron leaves a vacancy i.e. a missing electron in the covalent bond. This missing electron is called a \*hole which acts as a positive charge. For one electron set free, one hole is created. Therefore, thermal energy creates *hole-electron pairs*; there being as many holes as the free electrons. The current conduction by holes can be explained as follows:

The hole shows a missing electron. Suppose the valence electron at L (See Fig. 5.8) has become free electron due to thermal energy. This creates a hole in the co-valent bond at L. The hole is a strong centre of attraction \*\* for the electron. A valence electron (say at M) from nearby co-valent bond comes to fill in the hole at L. This results in the creation of hole at M. Another valence electron (say at N) in turn may leave its bond to fill the hole at M, thus creating a hole at N. Thus the hole having a positive charge has moved from L to N i.e. towards the negative terminal of supply. This constitutes hole current.

It may be noted that hole current is due to the movement of \*\*\*valence electrons from one covalent bond to another bond. The reader may wonder why to call it a hole current when the conduction is again by electrons (of course valence electrons!). The answer is that the basic reason for current flow is the presence of holes in the co-valent bonds. Therefore, it is more appropriate to consider the current as the movement of holes.

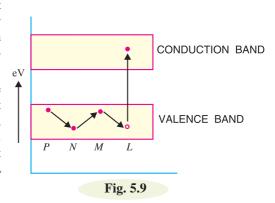

**Energy band description.** The hole current can be beautifully explained in terms of energy bands. Suppose due to thermal energy, an electron leaves the valence band to enter into the conduction band as shown in Fig. 5.9.

This leaves a vacancy at L. Now the valence electron at M comes to fill the hole at L. The result is that hole disappears at L and appears at M. Next, the valence electron at N moves into the hole at M. Consequently, hole is created at N. It is clear that valence electrons move along the path PNML whereas holes move in the opposite direction i.e. along the path LMNP.

- Note that hole acts as a virtual charge, although there is no physical charge on it.

- There is a strong tendency of semiconductor crystal to form co-valent bonds. Therefore, a hole attracts an electron from the neighbouring atom.

- \*\*\* Unlike the normal current which is by free electrons.

#### 5.8 Intrinsic Semiconductor

A semiconductor in an extremely pure form is known as an intrinsic semiconductor.

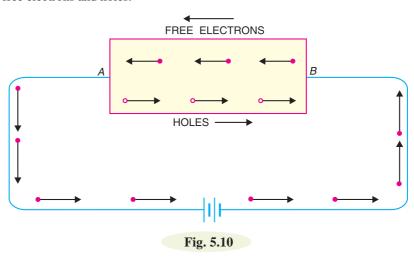

In an intrinsic semiconductor, even at room temperature, hole-electron pairs are created. When electric field is applied across an intrinsic semiconductor, the current conduction takes place by two processes, namely; by *free electrons* and *holes* as shown in Fig. 5.10. The free electrons are produced due to the breaking up of some covalent bonds by thermal energy. At the same time, holes are created in the covalent bonds. Under the influence of electric field, conduction through the semiconductor is by both free electrons and holes. Therefore, the total current inside the semiconductor is the sum of currents due to free electrons and holes.

It may be noted that current in the external wires is fully electronic i.e. by electrons. What about the holes? Referring to Fig. 5.10, holes being positively charged move towards the negative terminal of supply. As the holes reach the negative terminal B, electrons enter the semiconductor crystal near the terminal

and combine with holes, thus cancelling them. At the same time, the loosely held electrons near the positive terminal *A* are attracted away from their atoms into the positive terminal. This creates new holes near the positive terminal which again drift towards the negative terminal.

#### 5.9 Extrinsic Semiconductor

The intrinsic semiconductor has little current conduction capability at room temperature. To be useful in electronic devices, the pure semiconductor must be altered so as to significantly increase its conducting properties. This is achieved by adding a small amount of suitable impurity to a semiconductor. It is then called *impurity* or *extrinsic semiconductor*. The process of adding impurities to a semiconductor is known as *doping*. The amount and type of such impurities have to be closely controlled during the preparation of extrinsic semiconductor. Generally, for 10<sup>8</sup> atoms of semiconductor, one impurity atom is added.

The purpose of adding impurity is to increase either the number of free electrons or holes in the semiconductor crystal. As we shall see, if a pentavalent impurity (having 5 valence electrons) is added to the semiconductor, a large number of free electrons are produced in the semiconductor. On the other hand, addition of trivalent impurity (having 3 valence electrons) creates a large number of holes in the semiconductor crystal. Depending upon the type of impurity added, extrinsic semiconductors are classified into:

(i) n-type semiconductor (ii) p-type semiconductor

#### 5.10 *n*-type Semiconductor

When a small amount of pentavalent impurity is added to a pure semiconductor, it is known as **n-type semiconductor**.

The addition of pentavalent impurity provides a large number of free electrons in the semiconductor crystal. Typical examples of pentavalent impurities are arsenic (At. No. 33) and antimony (At. No. 51). Such impurities which produce n-type semiconductor are known as donor impurities because they donate or provide free electrons to the semiconductor crystal.

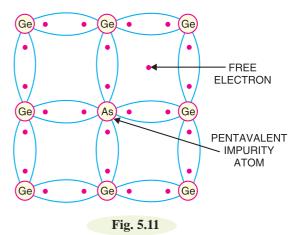

To explain the formation of *n*-type semiconductor, consider a pure germanium crystal. We know that germanium atom has four valence electrons. When a small amount of pentavalent impurity like arsenic is added to

germanium crystal, a large number of free electrons become available in the crystal. The reason is simple. Arsenic is pentavalent i.e. its atom has five valence electrons. An arsenic atom fits in the germanium crystal in such a way that its four valence electrons form covalent bonds with four germanium atoms. The *fifth* valence electron of arsenic atom finds no place in co-valent bonds and is thus free as shown in Fig. 5.11. Therefore, for each arsenic atom added, one free electron will be available in the germanium crystal. Though each arsenic atom provides one free electron, yet an extremely small amount of arsenic impurity provides enough atoms to supply millions of free electrons.

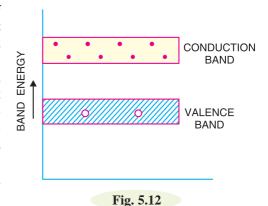

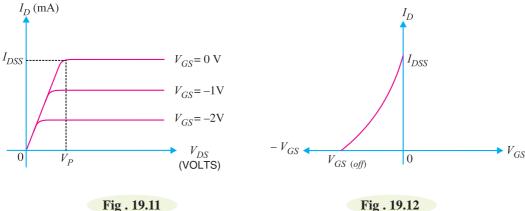

Fig. 5.12 shows the energy band description of *n*-type semi-conductor. The addition of pentavalent impurity has produced a number of conduction band electrons i.e., free electrons. The four valence electrons of pentavalent atom form covalent bonds with four neighbouring germanium atoms. The fifth left over valence electron of the pentavalent atom cannot be accommodated in the valence band and travels to the conduction band. The following points may be noted carefully:

(i) Many new free electrons are produced by the addition of pentavalent impurity.

(ii) Thermal energy of room temperature still generates a few hole-electron pairs. However, the number of free electrons provided by the pentavalent impurity far exceeds the number of holes. It is due to this predominance of electrons over holes that it is called n-type semiconductor (n stands for negative).

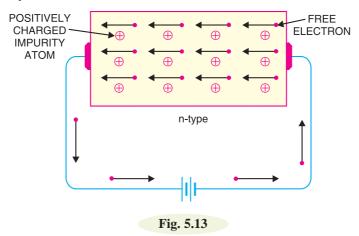

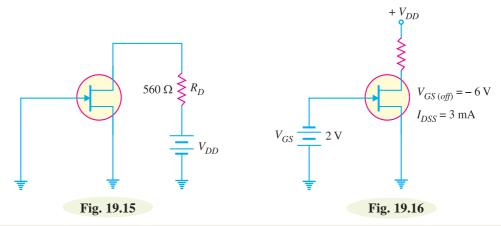

**n-type conductivity.** The current conduction in an *n*-type semiconductor is *predominantly* by free electrons i.e. negative charges and is called n-type or electron type conductivity. To understand n-type conductivity, refer to Fig. 5.13. When p.d. is applied across the n-type semiconductor, the free electrons (donated by impurity) in the crystal will be directed towards the positive terminal, constituting electric current. As the current flow through the crystal is by free electrons which are carriers of negative charge, therefore, this type of conductivity is called negative or *n*-type conductivity. It may be noted that conduction is just as in ordinary metals like copper.

#### 5.11 p-type Semiconductor

When a small amount of trivalent impurity is added to a pure semiconductor, it is called **p-type** semiconductor.

The addition of trivalent impurity provides a large number of holes in the semiconductor. Typical examples of trivalent impurities are *gallium* (At. No. 31) and *indium* (At. No. 49). Such impurities which produce *p*-type semiconductor are known as *acceptor impurities* because the holes created can accept the electrons.

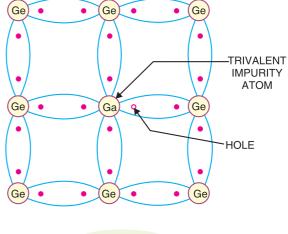

To explain the formation of p-type semiconductor, consider a pure germanium crystal. When a small amount of trivalent impurity like gallium is added to germanium crystal, there exists a large number of holes in the crystal. The reason is simple. Gallium is trivalent i.e. its atom has three valence electrons. Each atom of gallium fits into the germanium crystal but now only three co-valent bonds can be formed. It is because three valence electrons of gallium atom can form only three single co-valent bonds with three germanium atoms as shown in Fig. 5.14. In the fourth co-valent bond, only germanium atom contributes one valence electron while gallium has no valence

Fig. 5.14

electron to contribute as all its three valence electrons are already engaged in the co-valent bonds with neighbouring germanium atoms. In other words, fourth bond is incomplete; being short of one electron. This missing electron is called a *hole*. Therefore, for each gallium atom added, one hole is created. A small amount of gallium provides millions of holes.

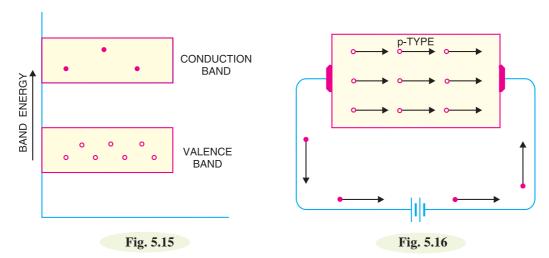

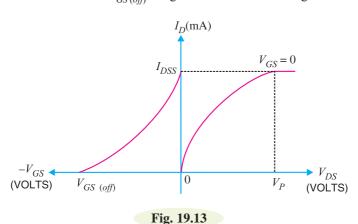

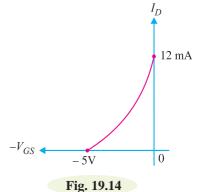

Fig. 5.15 shows the energy band description of the p-type semiconductor. The addition of trivalent impurity has produced a large number of holes. However, there are a few conduction band electrons due to thermal energy associated with room temperature. But the holes far outnumber the conduction band electrons. It is due to the predominance of holes over free electrons that it is called p-type semiconductor (p stands for positive).

**p-type conductivity.** The current conduction in *p*-type semiconductor is predominantly by holes *i.e.* positive charges and is called *p-type* or *hole-type conductivity*. To understand *p*-type conductivity, refer to Fig. 5.16. When *p.d.* is applied to the *p*-type semiconductor, the holes (donated by the impurity) are shifted from one co-valent bond to another. As the holes are positively charged, therefore, they are directed towards the negative terminal, constituting what is known as hole current. It may be noted that in *p*-type conductivity, the valence electrons move from one co-valent bond to another unlike the *n*-type where current conduction is by free electrons.

#### 5.12 Charge on *n*-type and *p*-type Semiconductors

As discussed before, in *n*-type semiconductor, current conduction is due to excess of electrons whereas in a *p*-type semiconductor, conduction is by holes. The reader may think that *n*-type material has a net negative charge and *p*-type a net positive charge. But this conclusion is wrong. It is true that *n*-type semiconductor has excess of electrons but these extra electrons were supplied by the atoms of donor impurity and each atom of donor impurity is electrically neutral. When the impurity atom is added, the term "excess electrons" refers to an excess with regard to the number of electrons needed to fill the co-valent bonds in the semiconductor crystal. The extra electrons are free electrons and increase the conductivity of the semiconductor. The situation with regard to *p*-type semiconductor is also similar. *It follows, therefore, that n-type as well as p-type semiconductor is electrically neutral.*

#### 5.13 Majority and Minority Carriers

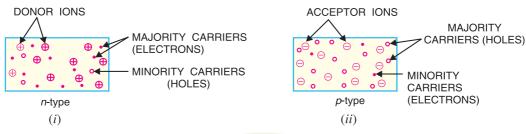

It has already been discussed that due to the effect of impurity, *n*-type material has a large number of free electrons whereas *p*-type material has a large number of holes. However, it may be recalled that even at room temperature, some of the co-valent bonds break, thus releasing an equal number of free electrons and holes. An *n*-type material has its share of electron-hole pairs (released due to breaking of bonds at room temperature) but in addition has a much larger quantity of free electrons due to the effect of impurity. These impurity-caused free electrons are not associated with holes. Consequently, an *n*-type material has a large number of free electrons and a small number of holes as shown in Fig. 5.17 (*i*). The free electrons in this case are considered *majority carriers* — since the majority portion of current in *n*-type material is by the flow of free electrons — and the holes are the *minority carriers*.

Similarly, in a p-type material, holes outnumber the free electrons as shown in Fig. 5.17 (ii). Therefore, holes are the majority carriers and free electrons are the minority carriers.

Fig. 5.17

#### 5.14 pn Junction

When a p-type semiconductor is suitably joined to n-type semiconductor, the contact surface is called pn junction.

Most semiconductor devices contain one or more pn junctions. The pn junction is of great importance because it is in effect, the *control element* for semiconductor devices. A thorough knowledge of the formation and properties of pn junction can enable the reader to understand the semiconductor devices.

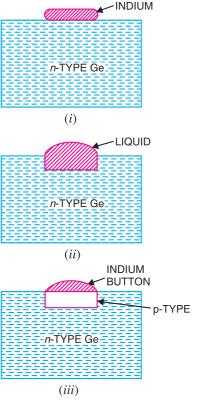

**Formation of** pn **junction.** In actual practice, the characteristic properties of pn junction will not be apparent if a p-type block is just brought in contact with n-type block. In fact, pn junction is fabricated by special techniques. One common method of making pn junction is called *alloying*. In this method, a small block of indium (trivalent impurity) is placed on an n-type germanium slab as shown in Fig. 5.18 (i). The system is then heated to a temperature of about 500°C. The indium and

some of the germanium melt to form a small puddle of molten germanium-indium mixture as shown in Fig. 5.18 (ii). The temperature is then lowered and puddle begins to solidify. Under proper conditions, the atoms of indium impurity will be suitably adjusted in the germanium slab to form a single crystal. The addition of indium overcomes the excess of electrons in the n-type germanium to such an extent that it creates a p-type region.

As the process goes on, the remaining molten mixture becomes increasingly rich in indium. When all germanium has been redeposited, the remaining material appears as indium button which is frozen on to the outer surface of the crystallised portion as shown in Fig. 5.18 (*iii*). This button serves as a suitable base for soldering on leads.

Fig. 5.18

#### 67

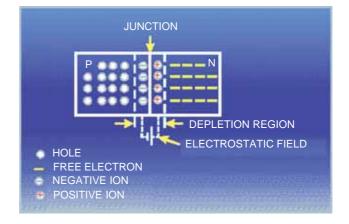

#### 5.15 Properties of pn Junction

At the instant of pn-junction formation, the free electrons near the junction in the n region begin to diffuse across the junction into the p region where they combine with holes near the junction. The result is that n region loses free electrons as they diffuse into the junction. This creates a layer of positive charges (pentavalent ions) near the junction. As the electrons move across the junction, the p region loses holes as the electrons and holes combine. The result is that there is a layer of negative charges (trivalent ions) near the junction. These two layers of positive and negative charges form the p depletion p region (or p depletion p layer). The term depletion is due to the fact that near the junction, the region is depleted (p emptied) of p charge p carries (free electrons and holes) due to diffusion across the junction. It may be noted that depletion layer is formed very quickly and is very thin compared to the p region and the p region. For clarity, the width of the depletion layer is shown exaggerated.

Once pn junction is formed and depletion layer created, the diffusion of free electrons stops. In other words, the depletion region acts as a barrier to the further movement of free electrons across the junction. The positive and negative charges set up an electric field. This is shown by a black arrow in Fig. 5.19 (i). The electric field is a barrier to the free electrons in the n-region. There exists a potential difference across the depletion layer and is called **barrier potential** ( $V_0$ ). The barrier potential of a pn junction depends upon several factors including the type of semiconductor material, the amount of doping and temperature. The typical barrier potential is approximately:

For silicon,  $V_0 = 0.7 \text{ V}$  ; For germanium,  $V_0 = 0.3 \text{ V}$

Fig. 5.20 shows the potential  $(V_0)$  distribution curve.

### 5.16 Applying D.C. Voltage Across *pn* Junction or Biasing a pn Junction

In electronics, the term bias refers to the use of d.c. voltage to establish certain operating conditions

for an electronic device. In relation to a pn junction, there are following two bias conditions:

- 1. Forward biasing

- 2. Reverse biasing

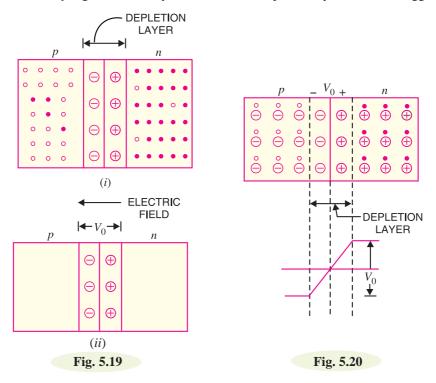

- **1. Forward biasing.** When external d.c. voltage applied to the junction is in such a direction that it cancels the potential barrier, thus permitting current flow, it is called **forward biasing.**

To apply forward bias, connect positive terminal of the battery to p-type and negative terminal to n-type as shown in Fig. 5.21. The applied forward potential establishes an electric field which acts against the field due to potential barrier. Therefore, the resultant field is weakened and the barrier height is reduced at the junction as shown in Fig. 5.21. As potential barrier voltage is very small (0.1 to 0.3 V), therefore, a small forward voltage is sufficient to completely eliminate the barrier. Once the potential barrier is eliminated by the forward voltage, junction resistance becomes almost zero and a low resistance path is established for the entire circuit. Therefore, current flows in the circuit. This is called *forward current*. With forward bias to pn junction, the following points are worth noting:

- (i) The potential barrier is reduced and at some forward voltage (0.1 to 0.3 V), it is eliminated altogether.

- (ii) The junction offers low resistance (called *forward resistance*,  $R_t$ ) to current flow.

- (iii) Current flows in the circuit due to the establishment of low resistance path. The magnitude of current depends upon the applied forward voltage.

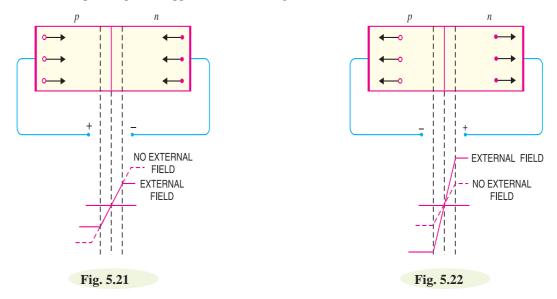

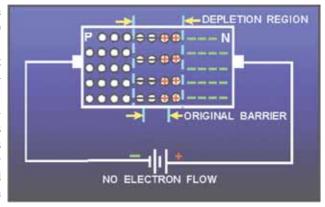

**2.** Reverse biasing. When the external d.c. voltage applied to the junction is in such a direction that potential barrier is increased, it is called reverse biasing.

To apply reverse bias, connect negative terminal of the battery to p-type and positive terminal to n-type as shown in Fig. 5.22. It is clear that applied reverse voltage establishes an electric field which acts in the same direction as the field due to potential barrier. Therefore, the resultant field at the junction is strengthened and the barrier height is increased as shown in Fig. 5.22. The increased potential barrier prevents the flow of charge carriers across the junction. Thus, a high resistance path is established for the entire circuit and hence the current does not flow. With reverse bias to pn junction, the following points are worth noting:

(i) The potential barrier is increased.

- (ii) The junction offers very high resistance (called reverse resistance, R.) to current flow.

- (iii) No current flows in the circuit due to the establishment of high resistance path.

Conclusion. From the above discussion, it follows that with reverse bias to the junction, a high resistance path is established and hence no current flow occurs. On the other hand, with forward bias to the junction, a low resistance path is set up and hence current flows in the circuit.

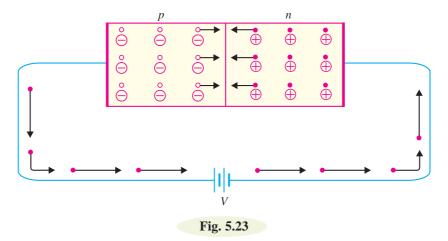

#### 5.17 Current Flow in a Forward Biased pn Junction

We shall now see how current flows across pn junction when it is forward biased. Fig. 5.23 shows a forward biased pn junction. Under the influence of forward voltage, the free electrons in n-type move \*towards the junction, leaving behind positively charged atoms. However, more electrons arrive from the negative battery terminal and enter the *n*-region to take up their places. As the free electrons reach the junction, they become \*\*valence electrons. As valence electrons, they move through the holes in the p-region. The valence electrons move towards left in the p-region which is equivalent to the holes moving to right. When the valence electrons reach the left end of the crystal, they flow into the positive terminal of the battery.

The mechanism of current flow in a forward biased pn junction can be summed up as under:

- (i) The free electrons from the negative terminal continue to pour into the n-region while the free electrons in the n-region move towards the junction.

- (ii) The electrons travel through the *n*-region as free-electrons i.e. current in *n*-region is by free electrons.

- Note that negative terminal of battery is connected to *n*-type. It repels the free electrons in *n*-type towards the junction.

- A hole is in the co-valent bond. When a free electron combines with a hole, it becomes a valence electron.

- (iii) When these electrons reach the junction, they combine with holes and become valence electrons.

- (iv) The electrons travel through p-region as valence electrons i.e. current in the p-region is by holes.

- ( $\nu$ ) When these valence electrons reach the left end of crystal, they flow into the positive terminal of the battery.

From the above discussion, it is concluded that in n-type region, current is carried by free electrons whereas in p-type region, it is carried by holes. However, in the external connecting wires, the current is carried by free electrons.

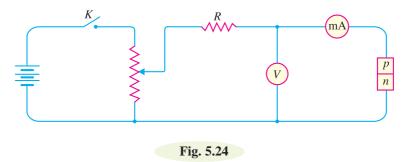

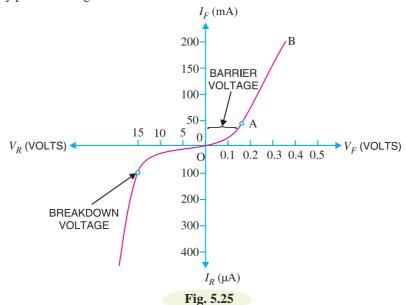

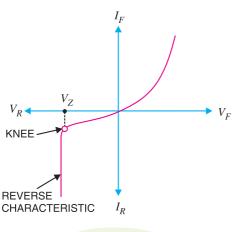

#### 5.18 Volt-Ampere Characteristics of pn Junction

Volt-ampere or *V-I* characteristic of a *pn* junction (also called a *crystal or semiconductor diode*) is the curve between voltage across the junction and the circuit current. Usually, voltage is taken along *x*-axis and current along *y*-axis. Fig. 5.24 shows the \*circuit arrangement for determining the *V-I* characteristics of a *pn* junction. The characteristics can be studied under three heads, namely; *zero external voltage*, *forward bias* and *reverse bias*.

(i) Zero external voltage. When the external voltage is zero, *i.e.* circuit is open at K, the potential barrier at the junction does not permit current flow. Therefore, the circuit current is zero as indicated by point O in Fig. 5.25.

\* R is the current limiting resistance. It prevents the forward current from exceeding the permitted value.

(ii) Forward bias. With forward bias to the pn junction i.e. p-type connected to positive terminal and n-type connected to negative terminal, the potential barrier is reduced. At some forward voltage (0.7 V for Si and 0.3 V for Ge), the potential barrier is altogether eliminated and current starts flowing in the circuit. From now onwards, the current increases with the increase in forward voltage. Thus, a rising curve OB is obtained with forward bias as shown in Fig. 5.25. From the forward characteristic, it is seen that at first (region OA), the current increases very slowly and the curve is non-linear. It is because the external applied voltage is used up in overcoming the potential barrier. However, once the external voltage exceeds the potential barrier voltage, the pn junction behaves like an ordinary conductor. Therefore, the current rises very sharply with increase in external voltage (region AB on the curve). The curve is almost linear.

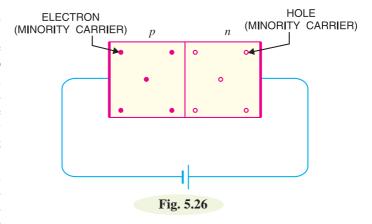

(iii) Reverse bias. With reverse bias to the pn junction i.e. p-type connected to negative terminal and *n*-type connected to positive terminal, potential barrier at the junction is increased. Therefore, the junction resistance becomes very high and practically no current flows through the circuit. However, in practice, a very small current (of the order of  $\mu A$ ) flows in the circuit with reverse bias as shown in the reverse

characteristic. This is called reverse \*saturation current  $(I_s)$  and is due to the minority carriers. It may be recalled that there are a few free electrons in p-type material and a few holes in n-type material. These undesirable free electrons in *p*-type and holes in *n*-type are called *minority carriers*. As shown in Fig. 5.26, to these minority carriers, the applied reverse bias appears as forward bias. Therefore, a \*\*small current flows in the reverse direction.

If reverse voltage is increased continuously, the kinetic energy of electrons (minority carriers) may become high enough to knock out electrons from the semiconductor atoms. At this stage breakdown of the junction occurs, characterised by a sudden rise of reverse current and a sudden fall of the resistance of barrier region. This may destroy the junction permanently.

**Note.** The forward current through a pn junction is due to the majority carriers produced by the impurity. However, reverse current is due to the *minority carriers* produced due to breaking of some co-valent bonds at room temperature.

#### 5.19 Important Terms

Two important terms often used with pn junction (i.e. crystal diode) are breakdown voltage and knee *voltage*. We shall now explain these two terms in detail.

(i) Breakdown voltage. It is the minimum reverse voltage at which pn junction breaks down with sudden rise in reverse current.

Under normal reverse voltage, a very little reverse current flows through a pn junction. However, if the reverse voltage attains a high value, the junction may break down with sudden rise in

- The term saturation comes from the fact that it reaches its maximum level quickly and does not significantly change with the increase in reverse voltage.

- Reverse current increases with reverse voltage but can generally be regarded as negligible over the working range of voltages.

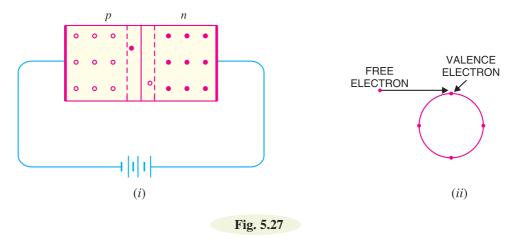

reverse current. For understanding this point, refer to Fig. 5.27. Even at room temperature, some hole-electron pairs (minority carriers) are produced in the depletion layer as shown in Fig. 5.27 (i). With reverse bias, the electrons move towards the positive terminal of supply. At large reverse voltage, these electrons acquire high enough velocities to dislodge valence electrons from semiconductor atoms as shown in Fig. 5.27 (ii). The newly liberated electrons in turn free other valence electrons. In this way, we get an *avalanche* of free electrons. Therefore, the *pn* junction conducts a very large reverse current.

Once the breakdown voltage is reached, the high reverse current may damage the junction. Therefore, care should be taken that reverse voltage across a *pn* junction is always less than the breakdown voltage.

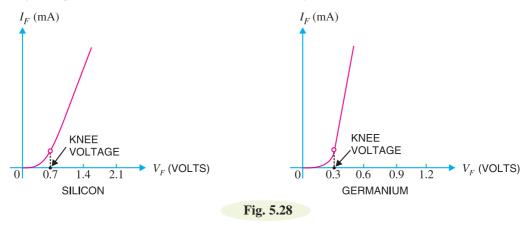

(ii) Knee voltage. It is the forward voltage at which the current through the junction starts to increase rapidly.

When a diode is forward biased, it conducts current very slowly until we overcome the potential barrier. For silicon *pn* junction, potential barrier is 0.7 V whereas it is 0.3 V for germanium junction. It is clear from Fig. 5.28 that knee voltage for silicon diode is 0.7 V and 0.3 V for germanium diode.

Once the applied forward voltage exceeds the knee voltage, the current starts increasing rapidly. It may be added here that in order to get useful current through a *pn* junction, the applied voltage must be more than the knee voltage.

**Note.** The potential barrier voltage is also known as *turn-on voltage*. This is obtained by taking the straight line portion of the forward characteristic and extending it back to the horizontal axis.

#### 5.20 Limitations in the Operating Conditions of pn Junction

Every pn junction has limiting values of maximum forward current, peak inverse voltage and maximum power rating. The pn junction will give satisfactory performance if it is operated within these limiting values. However, if these values are exceeded, the pn junction may be destroyed due to excessive heat.

- (i) Maximum forward current. It is the highest instantaneous forward current that a pn junction can conduct without damage to the junction. Manufacturer's data sheet usually specifies this rating. If the forward current in a pn junction is more than this rating, the junction will be destroyed due to overheating.

- (ii) Peak inverse voltage (PIV). It is the maximum reverse voltage that can be applied to the pn junction without damage to the junction. If the reverse voltage across the junction exceeds its PIV, the junction may be destroyed due to excessive heat. The peak inverse voltage is of particular importance in rectifier service. A pn junction i.e. a crystal diode is used as a rectifier to change alternating current into direct current. In such applications, care should be taken that reverse voltage across the diode during negative half-cycle of a.c. does not exceed the PIV of diode.

- W ar by

| (iii) Maximum power rating. It is the maximum power that can be dissipated at the junction ithout damaging it. The power dissipated at the junction is equal to the product of junction current at the voltage across the junction. This is a very important consideration and is invariably specified by the manufacturer in the data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MULTIPLE-CHOICE QUESTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| <ol> <li>A semiconductor is formed by bonds.         <ul> <li>(i) covalent</li> <li>(ii) electrovalent</li> <li>(iii) co-ordinate</li> <li>(iv) none of the above</li> </ul> </li> <li>A semiconductor has temperature coefficient of resistance.         <ul> <li>(i) positive</li> <li>(ii) zero</li> <li>(iii) negative</li> <li>(iv) none of the above</li> </ul> </li> <li>The most commonly used semiconductor is         <ul> <li>(i) germanium</li> <li>(ii) silicon</li> <li>(iii) carbon</li> <li>(iv) sulphur</li> </ul> </li> <li>A semiconductor has generally valence electrons.         <ul> <li>(i) 2</li> <li>(ii) 3</li> <li>(iii) 6</li> <li>(iv) 4</li> </ul> </li> <li>The resistivity of pure germanium under standard conditions is about         <ul> <li>(i) 6×10<sup>4</sup> Ω cm</li> <li>(ii) 60 Ω cm</li> <li>(iii) 3×10<sup>6</sup> Ω cm</li> <li>(iv) 6×10<sup>-4</sup> Ω cm</li> </ul> </li> <li>The resistivity of pure silicon is about         <ul> <li>(i) 100 Ω cm</li> <li>(ii) 6000 Ω cm</li> <li>(iii) 3×10<sup>5</sup> Ω cm</li> <li>(iv) 1.6×10<sup>-8</sup> Ω cm</li> </ul> </li> </ol> | <ul> <li>(iii) remains the same (iv) cannot say</li> <li>8. The strength of a semiconductor crystal comes from  (i) forces between nuclei  (ii) forces between protons  (iii) electron-pair bonds  (iv) none of the above</li> <li>9. When a pentavalent impurity is added to a pure semiconductor, it becomes  (i) an insulator  (ii) an intrinsic semiconductor  (iii) p-type semiconductor  (iv) n-type semiconductor</li> <li>10. Addition of pentavalent impurity to a semiconductor creates many  (i) free electrons  (ii) valence electrons  (iv) bound electrons</li> <li>11. A pentavalent impurity has valence electrons.  (i) 3 (ii) 5  (iii) 4 (iv) 6</li> </ul> |  |  |  |  |  |  |

| <b>7.</b> When a pure semiconductor is heated, its resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12. An <i>n</i> -type semiconductor is ( <i>i</i> ) positively charged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

(ii) negatively charged

(ii) goes down

(i) goes up

- (iii) electrically neutral

- (iv) none of the above

- 13. A trivalent impurity has ...... valence electrons.

- (*i*) 4

- (ii) 5

- (*iii*) 6

- (iv) 3

- 14. Addition of trivalent impurity to a semiconductor creates many ......

- (i) holes

- (ii) free electrons

- (iii) valence electrons

- (iv) bound electrons

- **15.** A hole in a semiconductor is defined as .......

- (i) a free electron

- (ii) the incomplete part of an electron pair

- (iii) a free proton

- (iv) a free neutron

- 16. The impurity level in an extrinsic semiconductor is about ...... of pure semiconductor.

- (i)  $10 \text{ atoms for } 10^8 \text{ atoms}$

- (ii) 1 atom for  $10^8$  atoms

- (iii) 1 atom for 10<sup>4</sup> atoms

- (iv) 1 atom for 100 atoms

- 17. As the doping to a pure semiconductor increases, the bulk resistance of the semiconductor .....

- (i) remains the same

- (ii) increases

- (iii) decreases

- (iv) none of the above

- 18. A hole and electron in close proximity would tend to ......

- (i) repel each other

- (ii) attract each other

- (iii) have no effect on each other

- (iv) none of the above

- 19. In a semiconductor, current conduction is due ......

- (i) only to holes

- (ii) only to free electrons

- (iii) to holes and free electrons

- (iv) none of the above

- 20. The random motion of holes and free electrons due to thermal agitation is called ......

- (i) diffusion

- (ii) pressure

- (iii) ionisation

- (iv) none of the above

- **21.** A forward biased *pn* junction has a resistance of the ......

- (i) order of  $\Omega$

- (ii) order of  $k\Omega$

- (iii) order of  $M\Omega$

- (iv) none of the above

- 22. The battery connections required to forward bias a pn junction are ......

- (i) +ve terminal to p and –ve terminal to n

- (ii) -ve terminal to p and +ve terminal to n

- (iii) –ve terminal to p and –ve terminal to n

- (iv) none of the above

- 23. The barrier voltage at a pn junction for germanium is about ......

- (i) 3.5 V

- (ii) 3V

- (iii) zero

- (iv) 0.3 V

- 24. In the depletion region of a pn junction, there is a shortage of ......

- (i) acceptor ions (ii) holes and electrons

- (iii) donor ions

- (iv) none of the above

- **25.** A reverse biased *pn* junction has .......

- (i) very narrow depletion layer

- (ii) almost no current

- (iii) very low resistance

- (iv) large current flow

- **26.** A *pn* junction acts as a .......

- (i) controlled switch

- (ii) bidirectional switch

- (iii) unidirectional switch

- (iv) none of the above

- **27.** A reverse biased pn junction has resistance of the.....

- (i) order of  $\Omega$

- (ii) order of  $k\Omega$

- (iii) order of M $\Omega$  (iv) none of the above

- **28.** The leakage current across a *pn* junction is due to ......

- (i) minority carriers

- (ii) majority carriers

- (iii) junction capacitance

- (iv) none of the above

- 29. When the temperature of an extrinsic semiconductor is increased, the pronounced effect is on ......

- (i) junction capacitance

- (ii) minority carriers

- (iii) majority carriers

- (iv) none of the above

- **30.** With forward bias to a pn junction, the width of depletion layer ......

- (i) decreases

- (ii) increases

- (iii) remains the same

- (iv) none of the above

- **31.** The leakage current in a pn junction is of the order of ......

- (*i*) A

- (ii) mA

- (iii) kA

- (iv) µA

- **32.** In an intrinsic semiconductor, the number of free electrons ......

- (i) equals the number of holes

- (ii) is greater than the number of holes

- (iii) is less than the number of holes

- (iv) none of the above

- 33. At room temperature, an intrinsic semiconductor has ......

- (i) many holes only

- (ii) a few free electrons and holes

- (iii) many free electrons only

- (iv) no holes or free electrons

- 34. At absolute temperature, an intrinsic semiconductor has ......

- (i) a few free electrons

- (ii) many holes

- (iii) many free electrons

- (iv) no holes or free electrons

- 35. At room temperature, an intrinsic silicon crystal acts approximately as ......

- (i) a battery

- (ii) a conductor

- (iii) an insulator

- (iv) a piece of copper wire

|                           | Answers 1                 | to Mult | iple-Ch    | oice Quest                | ions                      |

|---------------------------|---------------------------|---------|------------|---------------------------|---------------------------|

| <b>1.</b> ( <i>i</i> )    | <b>2.</b> ( <i>iii</i> )  | 3.      | (ii)       | <b>4.</b> ( <i>iv</i> )   | <b>5.</b> (ii)            |

| <b>6.</b> ( <i>ii</i> )   | <b>7.</b> (ii)            | 8.      | (iii)      | <b>9.</b> ( <i>iv</i> )   | <b>10.</b> ( <i>i</i> )   |

| <b>11.</b> ( <i>ii</i> )  | <b>12.</b> ( <i>iii</i> ) | 13.     | (iv)       | <b>14.</b> ( <i>i</i> )   | <b>15.</b> ( <i>ii</i> )  |

| <b>16.</b> ( <i>ii</i> )  | <b>17.</b> ( <i>iii</i> ) | 18.     | (ii)       | <b>19.</b> ( <i>iii</i> ) | <b>20.</b> ( <i>i</i> )   |

| <b>21.</b> ( <i>i</i> )   | <b>22.</b> ( <i>i</i> )   | 23.     | (iv)       | <b>24.</b> ( <i>ii</i> )  | <b>25.</b> ( <i>ii</i> )  |

| <b>26.</b> ( <i>iii</i> ) | <b>27.</b> ( <i>iii</i> ) | 28.     | <i>(i)</i> | <b>29.</b> ( <i>ii</i> )  | <b>30.</b> ( <i>i</i> )   |

| <b>31.</b> ( <i>iv</i> )  | <b>32.</b> ( <i>i</i> )   | 33.     | (ii)       | <b>34.</b> ( <i>iv</i> )  | <b>35.</b> ( <i>iii</i> ) |

#### **Chapter Review Topics**

- 1. What do you understand by a semi-conductor? Discuss some important properties of semiconductors.

- 2. Which are the most commonly used semiconductors and why?

- **3.** Give the energy band description of semiconductors.

- 4. Discuss the effect of temperature on semiconductors.

- 5. Give the mechanism of hole current flow in a semiconductor.

- **6.** What do you understand by intrinsic and extrinsic semiconductors?

- **7.** What is a pn junction? Explain the formation of potential barrier in a pn junction.

- **8.** Discuss the behaviour of a *pn* junction under forward and reverse biasing.

- **9.** Draw and explain the *V-I* characteristics of a *pn* junction.

- **10.** Write short notes on the following:

- (i) Breakdown voltage

- (ii) Knee voltage

- (iii) Limitations in the operating conditions of pn junction

#### **Discussion Questions**

- 1. Why is a semiconductor an insulator at ordinary temperature?

- **2.** Why are electron carriers present in *p*-type semiconductor ?

- 3. Why is silicon preferred to germanium in the manufacture of semiconductor devices?

- **4.** What is the importance of peak inverse voltage?

### 6

## Semiconductor Diode

- 6.1 Semiconductor Diode

- 6.3 Resistance of Crystal Diode

- 6.5 Crystal Diode Equivalent Circuits

- 6.7 Crystal Diode Rectifiers

- 6.9 Output Frequency of Half-Wave Rectifier

- 6.11 Full-Wave Rectifier

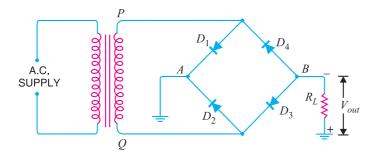

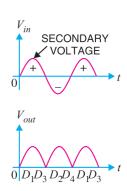

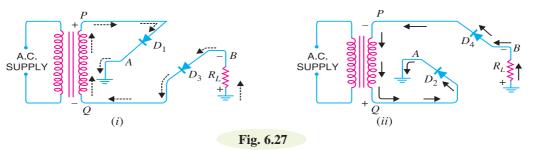

- 6.13 Full-Wave Bridge Rectifier

- 6.15 Efficiency of Full-Wave Rectifier

- 6.17 Nature of Rectifier Output

- 6.19 Comparison of Rectifiers

- 6.21 Types of Filter Circuits

- 6.23 Half-Wave Voltage Doubler

- 6.25 Zener Diode

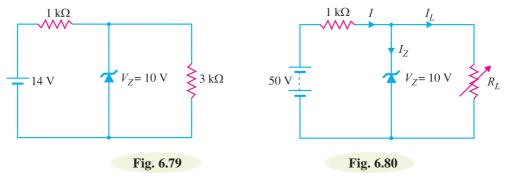

- 6.27 Zener Diode as Voltage Stabiliser

- 6.29 Crystal Diodes versus Vacuum Diodes

#### INTRODUCTION

t has already been discussed in the previous chapter that a *pn* junction conducts current easily when forward biased and practically no current flows when it is reverse biased. This unilateral conduction characteristic of *pn* junction (*i.e.* semiconductor diode) is similar to that of a vacuum diode. Therefore, like a vacuum diode, a semiconductor diode can also accomplish the job of *rectification i.e.* change alternating current to direct current. However, semiconductor diodes have become more \*popular as they are smaller in size, cheaper and robust and usually operate with greater efficiency. In this chapter, we shall focus our attention on the circuit performance and applications of semiconductor diodes.

\* On the other hand, vacuum diodes can withstand high reverse voltages and can operate at fairly high temperatures.

#### 6.1 Semiconductor Diode

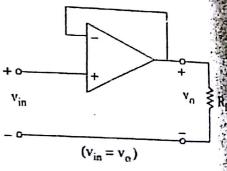

A pn junction is known as a semi-conductor or \*crystal diode.

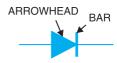

The outstanding property of a crystal diode to conduct current in one direction only permits it to be used as a rectifier. A crystal diode is usually represented by the schematic symbol shown in Fig. 6.1. The arrow in the symbol indicates the direction of easier conventional current flow.

A crystal diode has two terminals. When it is connected

Fig. 6.1

in a circuit, one thing to decide is whether the diode is forward or reverse biased. There is an easy rule to ascertain it. If the external circuit is trying to push the con-

ventional current in the direction of arrow, the diode is forward biased. On the other hand, if the conventional current is trying to flow opposite to arrowhead, the diode is reverse biased. Putting in simple words:

- (i) If arrowhead of diode symbol is positive w.r.t. bar of the symbol, the diode is forward biased.

- (ii) If the *arrowhead* of diode symbol is *negative w.r.t. bar*, the diode is reverse biased.

*Identification of crystal diode terminals*. While using a crystal diode, it is often necessary to know which end is arrowhead and which end is bar. For this purpose, the following methods are available:

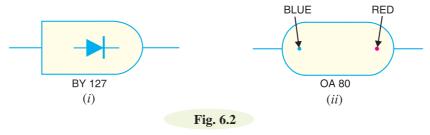

(i) Some manufacturers actually paint the symbol on the body of the diode *e.g. BY*127, *BY*114 crystal diodes manufactured by *BEL* [See Fig. 6.2 (i)].

(ii) Sometimes, red and blue marks are used on the body of the crystal diode. Red mark denotes arrow whereas blue mark indicates bar *e.g. OA80* crystal diode [See Fig. 6.2 (ii)].

#### 6.2 Crystal Diode as a Rectifier

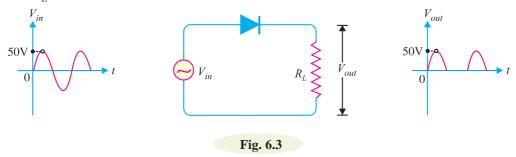

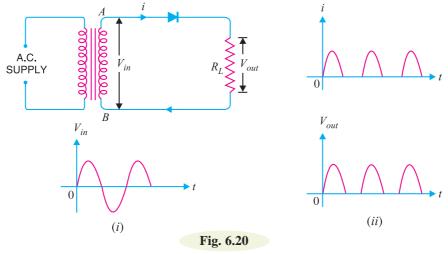

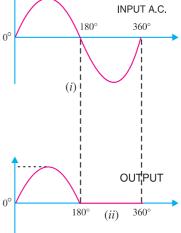

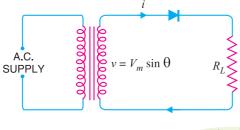

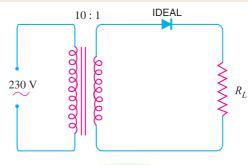

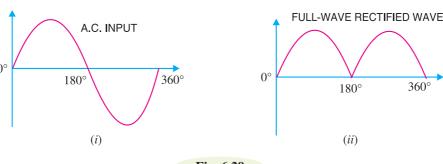

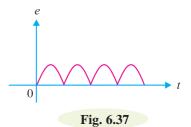

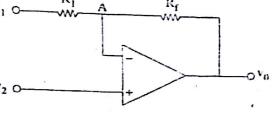

Fig. 6.3 illustrates the rectifying action of a crystal diode. The a.c. input voltage to be rectified, the diode and load  $R_L$  are connected in series. The d.c. output is obtained across the load as explained in the following discussion. During the positive half-cycle of a.c. input voltage, the arrowhead becomes positive w.r.t. bar. Therefore, diode is forward biased and conducts current in the circuit. The result is that positive half-cycle of input voltage appears across  $R_L$  as shown. However, during the negative half-cycle of input a.c. voltage, the diode becomes reverse biased because now the arrowhead is negative w.r.t. bar. Therefore, diode does not conduct and no voltage appears across load  $R_L$ . The result is that output consists of positive half-cycles of input a.c. voltage while the negative half-cycles are suppressed. In this way, crystal diode has been able to do rectification i.e. change a.c. into d.c. It may be seen that output across  $R_L$  is pulsating d.c.

\* So called because *pn* junction is grown out of a crystal.

It is interesting to see that behaviour of diode is like a *switch*. When the diode is forward biased, it behaves like a closed switch and connects the a.c. supply to the load  $R_L$ . However, when the diode is reverse biased, it behaves like an open switch and disconnects the a.c. supply from the load  $R_L$ . This switching action of diode permits only the positive half-cycles of input a.c. voltage to appear across  $R_L$ .

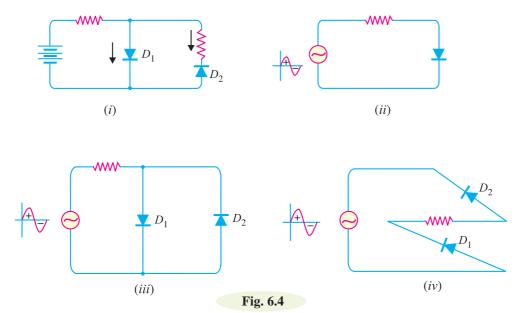

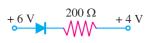

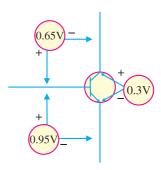

**Example 6.1.** In each diode circuit of Fig. 6.4, find whether the diodes are forward or reverse biased.

#### Solution.

- (i) Refer to Fig. 6.4 (i). The conventional current coming out of battery flows in the branch circuits. In diode  $D_1$ , the conventional current flows in the direction of arrowhead and hence this diode is forward biased. However, in diode  $D_2$ , the conventional current flows opposite to arrowhead and hence this diode is reverse biased.

- (ii) Refer to Fig. 6.4 (ii). During the positive half-cycle of input a.c. voltage, the conventional current flows in the direction of arrowhead and hence diode is forward biased. However, during the negative half-cycle of input a.c. voltage, the diode is reverse biased.

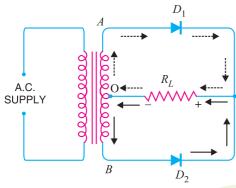

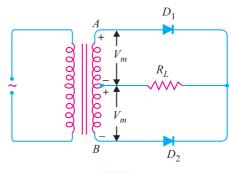

- (iii) Refer to Fig. 6.4 (iii). During the positive half-cycle of input a.c. voltage, conventional current flows in the direction of arrowhead in  $D_1$  but it flows opposite to arrowhead in  $D_2$ . Therefore, during positive half-cycle, diode  $D_1$  is forward biased and diode  $D_2$  reverse biased. However, during the negative half-cycle of input a.c. voltage, diode  $D_2$  is forward biased and  $D_1$  is reverse biased.

(iv) Refer to Fig. 6.4 (iv). During the positive half-cycle of input a.c. voltage, both the diodes are reverse biased. However, during the negative half-cycle of input a.c. voltage, both the diodes are forward biased.

#### 6.3 Resistance of Crystal Diode

It has already been discussed that a forward biased diode conducts easily whereas a reverse biased diode practically conducts no current. It means that *forward resistance* of a diode is quite small as compared with its reverse resistance.

- 1. Forward resistance. The resistance offered by the diode to forward bias is known as forward resistance. This resistance is not the same for the flow of direct current as for the changing current. Accordingly; this resistance is of two types, namely; d.c. forward resistance and a.c. forward resistance.

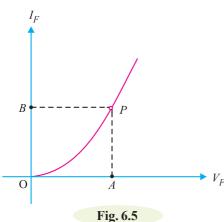

- (i) d.c. forward resistance. It is the opposition offered by the diode to the direct current. It is measured by the ratio of d.c. voltage across the diode to the resulting d.c. current through it. Thus, referring to the forward characteristic in Fig. 6.5, it is clear that when forward voltage is OA, the forward current is OB.

- d.c. forward resistance,  $R_f = \frac{OA}{OB}$

- (ii) a.c. forward resistance. It is the opposition offered by the diode to the changing forward current. It is measured by the ratio of change in voltage across diode to the resulting change in current through it i.e.

a.c. forward resistance,  $r_f = \frac{\text{Change in voltage across diode}}{\text{Corresponding change in current through diode}}$ Change in voltage across diode

Fig. 6.6

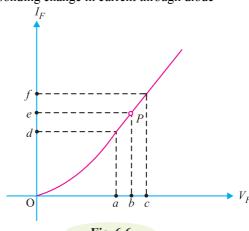

The a.c. forward resistance is more significant as the diodes are generally used with alternating voltages. The a.c. forward resistance can be determined from the forward characteristic as shown in Fig. 6.6. If P is the operating point at any instant, then forward voltage is ob and forward current is oe. To find the a.c. forward resistance, vary the forward voltage on both sides of the operating point equally as shown in Fig. 6.6 where ab = bc. It is clear from this figure that :

For forward voltage oa, circuit current is od.

For forward voltage oc, circuit current is of.

$$\therefore$$

a.c. forward resistance,  $r_f = \frac{\text{Change in forward voltage}}{\text{Change in forward current}} = \frac{oc - oa}{of - od} = \frac{ac}{df}$

It may be mentioned here that forward resistance of a crystal diode is very small, ranging from 1 to 25  $\Omega$ .

**Reverse resistance.** The resistance offered by the diode to the reverse bias is known as reverse resistance. It can be d.c. reverse resistance or a.c. reverse resistance depending upon whether the reverse bias is direct or changing voltage. Ideally, the reverse resistance of a diode is infinite. However, in practice, the reverse resistance is not infinite because for any value of reverse bias, there does exist a small leakage current. It may be emphasised here that reverse resistance is very large compared to the forward resistance. In germanium diodes, the ratio of reverse to forward resistance is 40000: 1 while for silicon this ratio is 1000000: 1.

#### 6.4 Equivalent Circuit of Crystal Diode

It is generally profitable to replace a device or system by its equivalent circuit. An equivalent circuit of a device (e.g. crystal diode, transistor etc.) is a combination of electric elements, which when connected in a circuit, acts exactly as does the device when connected in the same circuit. Once the device is replaced by its equivalent circuit, the resulting network can be solved by traditional circuit analysis techniques. We shall now find the equivalent circuit of a crystal diode.

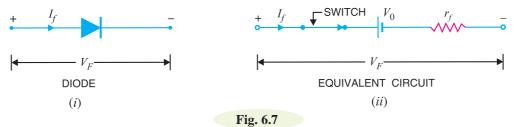

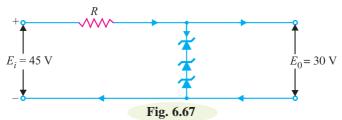

- (i) \*Approximate Equivalent circuit. When the forward voltage  $V_F$  is applied across a diode, it will not conduct till the potential barrier  $V_0$  at the junction is overcome. When the forward voltage exceeds the potential barrier voltage, the diode starts conducting as shown in Fig. 6.7 (i). The forward current  $I_f$  flowing through the diode causes a voltage drop in its internal resistance  $r_f$ . Therefore, the forward voltage  $V_F$  applied across the *actual* diode has to overcome:

- (a) potential barrier  $V_0$

- (b) internal drop  $I_f r_f$

$$V_F = V_0 + I_f r_f$$

$V_F = V_0 + I_f r_f$  For a silicon diode,  $V_0$  = 0.7 V whereas for a germanium diode,  $V_0$  = 0.3 V.

Therefore, approximate equivalent circuit for a crystal diode is a switch in series with a battery  $V_0$  and internal resistance  $r_f$  as shown in Fig. 6.7 (ii). This approximate equivalent circuit of a diode is very helpful in studying the performance of the diode in a circuit.

(ii) Simplified Equivalent circuit. For most applications, the internal resistance  $r_f$  of the crystal diode can be ignored in comparison to other elements in the equivalent circuit. The equivalent circuit then reduces to the one shown in Fig. 6.8 (ii). This simplified equivalent circuit of the crystal diode is frequently used in diode-circuit analysis.

We assume here that V/I characteristic of crystal diode is linear.

(iii) Ideal diode model. An ideal diode is one which behaves as a perfect conductor when forward biased and as a perfect insulator when reverse biased. Obviously, in such a hypothetical situation, forward resistance  $r_f = 0$  and potential barrier  $V_0$  is considered negligible. It may be mentioned here that although ideal diode is never found in practice, yet diode circuit analysis is made on this basis. Therefore, while discussing diode circuits, the diode will be assumed ideal unless and until stated otherwise.

#### 6.5 Crystal Diode Equivalent Circuits

It is desirable to sum up the various models of crystal diode equivalent circuit in the tabular form given below:

| S.No. | Type              | Model                                         | Characteristic                                                                |  |

|-------|-------------------|-----------------------------------------------|-------------------------------------------------------------------------------|--|

| 1.    | Approximate model | + V <sub>0</sub> r <sub>f</sub> - IDEAL DIODE | $ \begin{array}{c c}  & I_F \\ \hline  & / \\ \hline  & 0 & V_0 \end{array} $ |  |

| 2.    | Simplified model  | † V <sub>0</sub>                              | $\begin{array}{c c} & I_F \\ \hline 0 & V_0 \end{array} \longrightarrow V_F$  |  |

| 3.    | Ideal Model       | † - IDEAL DIODE                               | $\bigcup_{0}^{I_{F}}$                                                         |  |

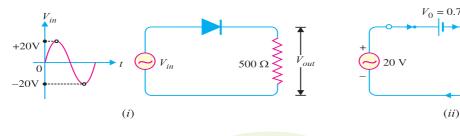

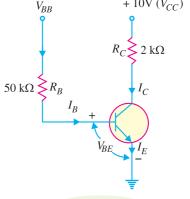

**Example 6.2.** An a.c. voltage of peak value 20 V is connected in series with a silicon diode and load resistance of 500  $\Omega$ . If the forward resistance of diode is 10  $\Omega$ , find:

(i) peak current through diode

(ii) peak output voltage

What will be these values if the diode is assumed to be ideal?

#### Solution.

Peak input voltage = 20 V

Forward resistance,  $r_f = 10 \Omega$

Load resistance,  $R_L = 500 \Omega$

Potential barrier voltage,  $V_0 = 0.7 \text{ V}$

The diode will conduct during the positive half-cycles of a.c. input voltage only. The equivalent circuit is shown in Fig. 6.9 (ii).

Fig. 6.9

(i) The peak current through the diode will occur at the instant when the input voltage reaches positive peak i.e.  $V_{in} = V_F = 20 \text{ V}$ .

$$V_F = V_0 + (I_f)_{peak} [r_f + R_L] \qquad ...(i)$$

or

$$(I_f)_{peak} = \frac{V_F - V_0}{r_f + R_L} = \frac{20 - 0.7}{10 + 500} = \frac{19.3}{510} \text{ A} = 37.8 \text{ mA}$$

(ii) Peak output voltage =  $(I_f)_{peak} \times R_L = 37.8 \text{ mA} \times 500 \Omega = 18.9 \text{ V}$

**Ideal diode.** For an ideal diode, put  $V_0 = 0$  and  $r_f = 0$  in equation (i).

$$V_F = (I_f)_{peak} \times R_L$$

or

$$(I_f)_{peak} = \frac{V_F}{R_L} = \frac{20 \text{ V}}{500 \Omega} = 40 \text{ mA}$$

Peak output voltage =  $(I_f)_{peak} \times R_L = 40 \text{ mA} \times 500 \Omega = 20 \text{ V}$

**Comments.** It is clear from the above example that output voltage is *nearly* the same whether the actual diode is used or the diode is considered ideal. This is due to the fact that input voltage is quite large as compared with  $V_0$  and voltage drop in  $r_f$ . Therefore, nearly the whole input forward voltage appears across the load. For this reason, diode circuit analysis is generally made on the ideal diode basis.

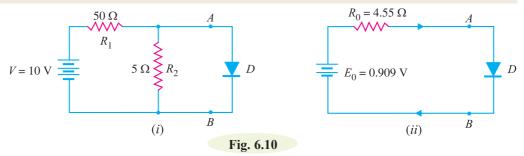

**Example 6.3.** Find the current through the diode in the circuit shown in Fig. 6.10 (i). Assume the diode to be ideal.

**Solution.** We shall use Thevenin's theorem to find current in the diode. Referring to Fig. 6.10(*i*),

$E_0$  = Thevenin's voltage

= Open circuited voltage across AB with diode removed

$$= \frac{R_2}{R_1 + R_2} \times V = \frac{5}{50 + 5} \times 10 = 0.909 \,\mathrm{V}$$

$R_0$  = Thevenin's resistance

= Resistance at terminals AB with diode removed and battery replaced by a short circuit

$$= \frac{R_1 R_2}{R_1 + R_2} = \frac{50 \times 5}{50 + 5} = 4.55 \Omega$$

Fig. 6.10 (ii) shows Thevenin's equivalent circuit. Since the diode is ideal, it has zero resistance.

: Current through diode =

$$\frac{E_0}{R_0} = \frac{0.909}{4.55} = 0.2 \text{ A} = 200 \text{ mA}$$

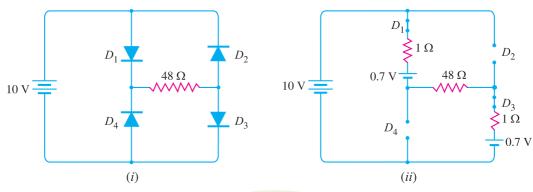

**Example 6.4.** Calculate the current through 48  $\Omega$  resistor in the circuit shown in Fig. 6.11 (i). Assume the diodes to be of silicon and forward resistance of each diode is 1  $\Omega$ .

**Solution.** Diodes  $D_1$  and  $D_3$  are forward biased while diodes  $D_2$  and  $D_4$  are reverse biased. We can, therefore, consider the branches containing diodes  $D_2$  and  $D_4$  as "open". Replacing diodes  $D_1$  and  $D_3$  by their equivalent circuits and making the branches containing diodes  $D_2$  and  $D_4$  open, we get the circuit shown in Fig. 6.11 (ii). Note that for a silicon diode, the barrier voltage is 0.7 V.

Fig. 6.11

Net circuit voltage =

$$10 - 0.7 - 0.7 = 8.6 \text{ V}$$

Total circuit resistance =

$$1 + 48 + 1 = 50 \Omega$$

:. Circuit current =

$$8.6/50 = 0.172 \text{ A} = 172 \text{ mA}$$

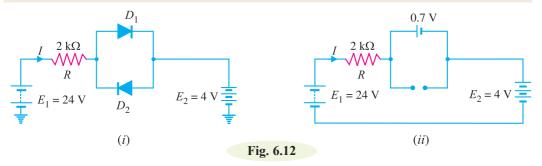

**Example 6.5.** Determine the current I in the circuit shown in Fig. 6.12 (i). Assume the diodes to be of silicon and forward resistance of diodes to be zero.

**Solution.** The conditions of the problem suggest that diode  $D_1$  is forward biased and diode  $D_2$  is reverse biased. We can, therefore, consider the branch containing diode  $D_2$  as open as shown in Fig. 6.12 (ii). Further, diode  $D_1$  can be replaced by its simplified equivalent circuit.

$$I = \frac{E_1 - E_2 - V_0}{R} = \frac{24 - 4 - 0.7}{2 \text{ k}\Omega} = \frac{19.3 \text{ V}}{2 \text{ k}\Omega} = 9.65 \text{ mA}$$

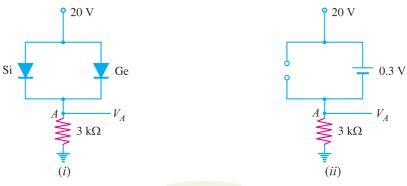

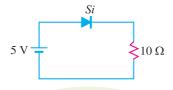

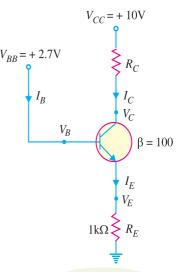

**Example 6.6.** Find the voltage  $V_A$  in the circuit shown in Fig. 6.13 (i). Use simplified model.

Fig. 6.13

**Solution.** It appears that when the applied voltage is switched on, both the diodes will turn "on". But that is not so. When voltage is applied, germanium diode ( $V_0 = 0.3 \text{ V}$ ) will turn on first and a level of 0.3 V is maintained across the parallel circuit. The silicon diode never gets the opportunity to have 0.7 V across it and, therefore, remains in open-circuit state as shown in Fig. 6.13 (ii).

$$V_A = 20 - 0.3 = 19.7 \text{ V}$$

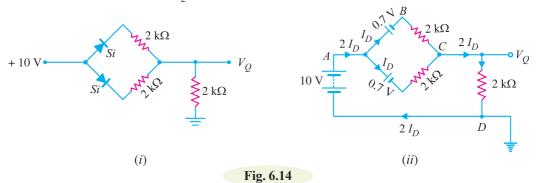

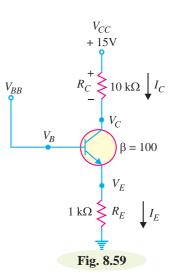

**Example 6.7.** Find  $V_O$  and  $I_D$  in the network shown in Fig. 6.14 (i). Use simplified model.

**Solution.** Replace the diodes by their simplified models. The resulting circuit will be as shown in Fig. 6.14 (ii). By symmetry, current in each branch is  $I_D$  so that current in branch CD is  $2I_D$ . Applying Kirchhoff's voltage law to the closed circuit ABCDA, we have,

$$-0.7 - I_D \times 2 - 2I_D \times 2 + 10 = 0$$

or

$$6I_D = 9.3$$

$$\therefore I_D = \frac{9.3}{6} = 1.55 \text{ mA}$$

Also

$$V_Q = (2I_D) \times 2 \text{ k}\Omega = (2 \times 1.55 \text{ mA}) \times 2 \text{ k}\Omega = 6.2 \text{ V}$$

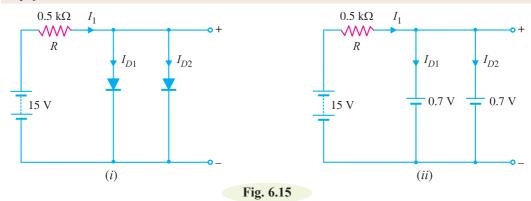

**Example 6.8.** Determine current through each diode in the circuit shown in Fig. 6.15 (i). Use simplified model. Assume diodes to be similar.

**Solution.** The applied voltage forward biases each diode so that they conduct current in the same direction. Fig. 6.15 (*ii*) shows the equivalent circuit using simplified model. Referring to Fig. 6.15 (*ii*),

$$I_1 = \frac{\text{Voltage across } R}{R} = \frac{15 - 0.7}{0.5 \text{ k}\Omega} = 28.6 \text{ mA}$$

Since the diodes are similar,  $I_{D1} = I_{D2} = \frac{I_1}{2} = \frac{28.6}{2} = 14.3 \text{ mA}$

Comments. Note the use of placing the diodes in parallel. If the current rating of each diode is 20

20 mA and a single diode is used in this circuit, a current of 28.6 mA would flow through the diode, thus damaging the device. By placing them in parallel, the current is limited to a safe value of 14.3 mA for the same terminal voltage.

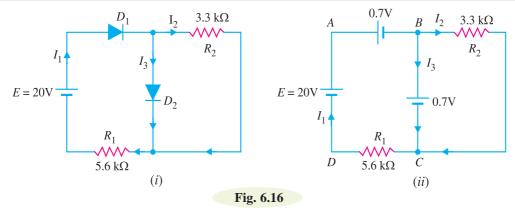

**Example 6.9.** Determine the currents  $I_1$ ,  $I_2$  and  $I_3$  for the network shown in Fig. 6.16(i). Use simplified model for the diodes.

**Solution.** An inspection of the circuit shown in Fig. 6.16 (i) shows that both diodes  $D_1$  and  $D_2$  are forward biased. Using simplified model for the diodes, the circuit shown in Fig. 6.16 (i) becomes the one shown in Fig. 6.16 (ii). The voltage across  $R_2$  (= 3.3 k  $\Omega$ ) is 0.7V.

:.

$$I_2 = \frac{0.7 \text{ V}}{3.3 \text{ k}\Omega} = 0.212 \text{ mA}$$

Applying Kirchhoff's voltage law to loop ABCDA in Fig. 6.16 (ii), we have,

$$-0.7 - 0.7 - I_1 R_1 + 20 = 0$$

$$I_1 = \frac{20 - 0.7 - 0.7}{R_1} = \frac{18.6 \text{ V}}{5.6 \text{ k}\Omega} = 3.32 \text{ mA}$$

Now

$$I_1 = I_2 + I_3$$

$$I_3 = I_1 - I_2 = 3.32 - 0.212 = 3.108 \text{ mA}$$

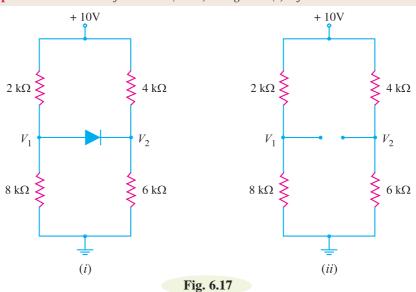

**Example 6.10.** Determine if the diode (ideal) in Fig. 6.17 (i) is forward biased or reverse biased.

**Solution.** Let us assume that diode in Fig. 6.17 (*i*) is *OFF i.e.* it is reverse biased. The circuit then becomes as shown in Fig. 6.17 (*ii*). Referring to Fig. 6.17 (*ii*), we have,

$$V_1 = \frac{10 \text{ V}}{2 \text{ k}\Omega + 8 \text{ k}\Omega} \times 8 \text{ k}\Omega = 8\text{V}$$

$$V_2 = \frac{10 \text{ V}}{4 \text{ k}\Omega + 6 \text{ k}\Omega} \times 6 \text{ k}\Omega = 6\text{V}$$

$\therefore$  Voltage across diode =  $V_1 - V_2 = 8 - 6 = 2V$

Now  $V_1 - V_2 = 2V$  is enough voltage to make the diode *forward biased*. Therefore, our initial assumption was wrong.

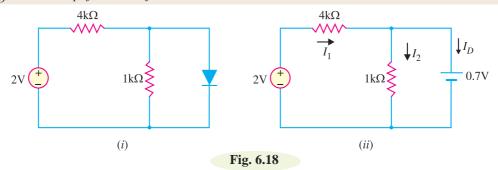

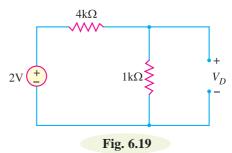

**Example 6.11.** Determine the state of diode for the circuit shown in Fig. 6.18 (i) and find  $I_D$  and  $V_D$ . Assume simplified model for the diode.

**Solution.** Let us assume that the diode is *ON*. Therefore, we can replace the diode with a 0.7V battery as shown in Fig. 6.18 (*ii*). Referring to Fig. 6.18 (*ii*), we have,

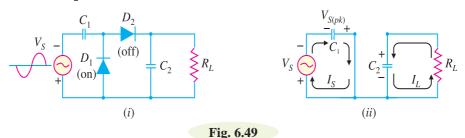

$$I_1 = \frac{(2 - 0.7) \text{ V}}{4 \text{ k}\Omega} = \frac{1.3 \text{ V}}{4 \text{ k}\Omega} = 0.325 \text{ mA}$$